朋友们、您好!

为 OneShot 中断超时事件配置 GPTM3全宽 、并在 中断处理程序周期内重新加载1秒的值。

GPTM3 CLK 源: 16MHz PIOSC (65.5ns)

加载值:0xF42400 (16、000、000 * 65.5ns = 1秒单次触发间隔)

问题是 、通过示波器探针测得的一次性周期 GPIO 端口 (1sec) 间隔 在 PWM0激活前保持稳定。 单次触发加载时间中断开始加宽 >1.1秒(>100ms), 这似乎取决于 PWM0在占空比更新中被中断的频率。 为什么加载值不能使中断周期与递减计数 超时 过期相当一致? 在递减计数计时器 加载值过期 并触发矢量中断处理程序中、这似乎是一种奇数勘误表。 OneShot 在 边沿计数计时器 CCP 中断事件中启用。 在 这种情况下、我们实际上并不关心边沿计数中断的发生频率。 但是、在 前一个计数 到期之前、不要相信 OneShot 应该允许或处理计数重新加载。

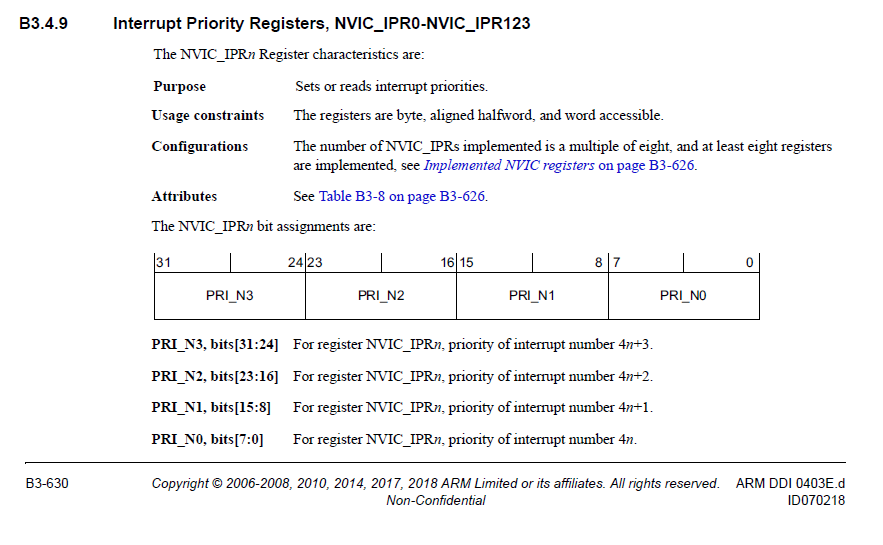

期望重新加载周期漂移小于16.6ns (<2 x SYSCLK (8.3ns))、NVIC 运行频率为120MHz 是否合理? 是否有办法使 确切 的1秒时间间隔 不受其他中断源的影响? 当 GPTM 时钟 为120MHz 时、漂移中断处理程序(>100ms)杂散甚至更宽。 在 INT 矢量调用/处理程序之外重新加载一次性加载值是否更好? 如果 OneShot 间隔大于100ms 的重新加载值在进程中不包含,则会出现奇数。