大家好、

我想以比两个 ADC 的有效采样率更高的采样率对一些信号进行采样(例如、我不想使用1MHz 的最大采样率、而是希望以1.5-3MHz 的频率进行采样)。 我知道采样相位控制的可能性、但由于我有多个信号、我认为我无法使用它。

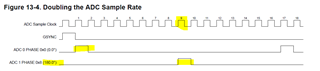

根据 关于堆叠溢出的本主题 、如果 ADC 通过通道进行排序、则可以使用 ADC 的多个通道在给定 ADC 的最大采样率范围内提高有效采样率。

我的问题是、是否可以"回顾"此 ADC 的1MSPS (1MHz)采样率、如果是、此 uC 上的 ADC 的哪些设置允许这样做(使用采样相位控制除外)?

感谢您提前回答、

此致、

Zsolt