主题中讨论的其他器件:EK-TM4C123GXL

您好!

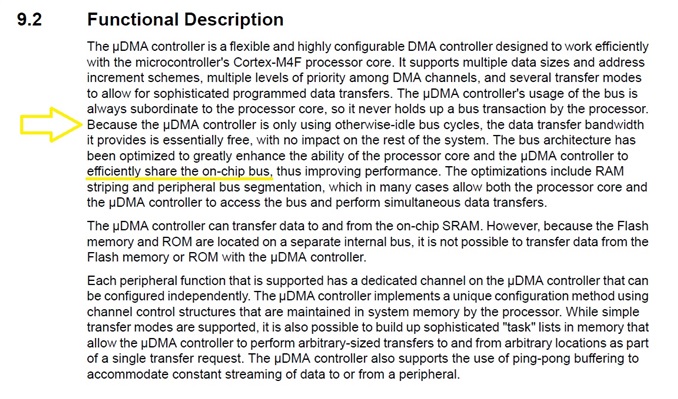

有一个关于 uDMA 和 CPU 如何共享总线的一般问题。 我一直在阅读数据表、力图绕过这个问题。 在下面所示的第9.2节"功能说明"中表示 uDMA 使用 备用 之间的空闲时间。 我很难更好地理解这意味着什么、尤其是在 SSI RX FIFO 中乒乓数据块到存储块的用例中、这也是我的用例。

我的应用将 CPU 置于主循环中、检查存储器中的变量、而 uDMA 应将数据从 SSI RS 移动到仲裁大小为4字节的存储器区域。 我认为 CPU 和 uDMA 共享同一条总线到存储器、因此我的问题如下。

1.在 CPU 不运行时 DMA 只访问内存吗? 因此、如果我不断轮询 RAM 中的标志、这是否会由于读取标志(存储器位置)而抑制 DMA 的性能?

2.如何知道 CPU 何时对 DMA 进行节流或者反之? 我在这里感到困惑、因为我已读取它们共享一条总线、但 uDMA 通常使用备用的 CPU 周期?

谢谢