主题中讨论的其他器件:HALCOGEN

您好!

我正在一个项目上、并启用了一些中断(使用 IRQ 启用了 SCI 和 SCI2、使用 FIQ 启用了 RTI Comparex)。 我正在研究如何为 ADC 奇偶校验错误添加一个 ESM 低电平中断处理程序、但我发现有些令人困惑的行为。 RTI 被用来为主循环中的函数执行设定标志、此标志的时序十分可靠、直到我在 VIM 中启用 ESM 低中断处理程序。 一旦我启用此功能、似乎就会中断正常执行方案。

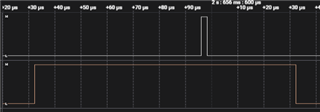

使用 ADC 的函数通常以~70us 或40微秒左右的速度执行、其中的 HalCoGen 表示为所使用通道的采样和转换时间。 一旦 ESM 低中断被启用、这个执行时间将膨胀到大于1ms。

其他时序也会发生类似的改动。 好像在 FIQ 中执行的 RTI 中断本身的执行时间要长得多。

虽然我认为我已经将配置更改隔离为启用 ESM 低中断、但是我已经在父代码库(其 RTI 中断位于 IRQ 中、但是没有启用很多启动测试)上启用了它、而且没有对时序进行类似的更改。

有什么想法,为什么会发生这种情况? 我在 TRM 中没有看到任何关于使用 ESM 低电平中断的提及、它对系统中的时序有什么影响、 根据我的理解、在 IRQ 中启用 ESM 低电平中断似乎并不常见、这会对 FIQ 中 RTI 的执行产生任何影响