主题中讨论的其他器件:TMS570LC4357、

尊敬的 TI 团队:

1. 我将尝试通过以下线程中建议的方式更改链接器脚本文件、从 SDRAM 执行代码。

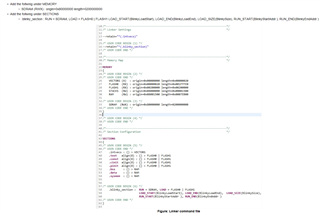

我当前修改的脚本文件如下:

/ /

/*禁止警告和错误:*/

/*#10199-D CRC 表运算符(crc_table_for_<>)已忽略:

CRC table 运算符无法与空输出段关联*/

--diag_suppress=10199

--retain=interruptVectors

#define APP_BASE 0x60000000

#define RAM_BASE 0x60100000

内存

{

FLASH (RX):origin = APP_BASE,length = 0x00100000

SRAM (rwx):origin = RAM_BASE、length = 0x00040000

}

/*以下命令行选项作为 CCS 项目的一部分设置。 */

/*如果您正在使用命令行进行构建,或者出于某种原因想要*/

/*在此处定义它们,您可以根据需要取消注释和修改这些行。 */

/*如果您使用 CCS 进行构建、则最好制作任何此类项目*/

/*对 CCS 项目的修改,并保留该文件。 */

/**/

/*--heap_size=0 */

/*--stack_size=256 */

/*--library=rtsv7M4_T_le_eabi.lib */

/*内存中的段分配*/

部分

{

#ifndef gen_crc_table

.intvecs:> app_base

.text :>闪存

.const :>闪存

cinit :>闪存

请输入您的密码:> FLASH

.rodata :>闪存

init_array:> FLASH

#else

.intvecs:> 0x00000000、crc_table (crc_table_for_intvecs)

.text:> flash、crc_table (crc_table_for_text)

.const:> FLASH、crc_table (crc_table_for_const)

.cinit:> flash、crc_table (crc_table_for_cinit)

.pinit:> FLASH、crc_table (crc_table_for_Pinit)

.rodata:> FLASH、crc_table (crc_table_for_Pinit)

init_array:> FLASH、crc_table (crc_table_for_init_array)

.TI.crctab:>闪存

#endif

.vtable:> RAM_BASE

.data :> SRAM

bss :> SRAM

.sysmem:> SRAM

.stack:> SRAM

}

__STACK_TOP =_STACK + 512;

******************* /

1.将.out 文件数据复制到 SDRAM 后,我将调用下面的函数。

******************* /

uint32 entryPiont;

entryPiont = 0x60000000;//SDRAM 存储器地址

appEntry =(void (*)(void)) entryPiont;

(* appEntry)();

***************** /

2.代码未按预期从 SDRAM 执行。

3.是否需要在链接程序脚本或更高级别的函数中进行任何修改?

此致、

Naga Narasimha Rao P