大家好、

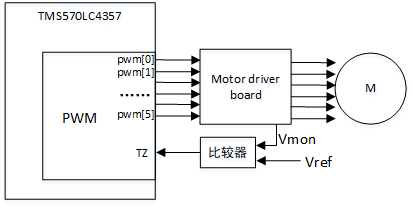

使用 PWM 驱动无刷三相电机时、使用模拟比较芯片监测电机驱动板电压、并连接到 PWM 的 TZ 输入:

信号由示波器捕获、模拟比较器输出到 PWM TZ 的信号上存在干扰、并且在每个 PWM 周期中、干扰在非固定位置发生。 客户希望通过 PWM 中数字比较模块 DC 的过滤功能来过滤 TZ 上的毛刺脉冲。

根据 TMS570LC4357 PWM 模块直流 部分、假设 T1和 T2是两个相邻的 PWM 周期(T2在 T1时间之后):

- 在偏移计数器递减至0之后、窗口计数器开始计数

- 窗口范围内的毛刺被过滤

- DCCAP 寄存器捕获发生 DCEVFILT 事件时的时基计数器值。

基于上述前提、假设瞬发性波动在 T1时间发生在 TZ 信号的中间、 首先、软件需要设置直流捕捉、然后读取 DCCAP 寄存器的值、从而使用在 DCCAP 中捕获的时基计数器的值设置下图中的偏移长度。 窗口范围也根据干扰的宽度设置、以便窗口滤波器范围涵盖发生干扰的区域、以过滤干扰。 不过、如果 TZ 信号上干扰的位置在下一个周期(T2时间)发生变化、例如、干扰会在 TZ 之后的区域中发生、因为配置的 T1时间偏移和窗口不能满足 T2时间、 导致 在 T1时间配置的滤波器间隔无法滤除 T2时间的干扰。

1) 1) PWM 模块中的直流滤波器干扰功能是否仅支持滤除固定在 TZ 信号上的干扰?

2) 如果每个干扰的宽度不同、软件应如何动态调整窗口计数器值以覆盖发生干扰的区域?

您能帮助检查这个问题吗? 谢谢。

此致、

切里