主题中讨论的其他器件:AM2732、 SysConfig

您好专家

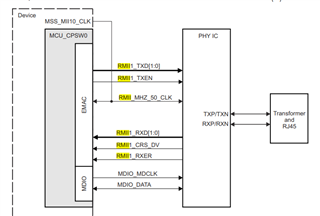

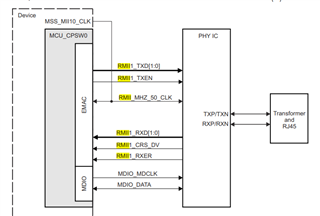

当 AM2732配置为 RMII 模式时、我们需要将 RMII_MHz_50_CLK 输出到 CPSW 和 PHY。

我们可以使用 RMII_ref_clk_OE_n 来选择可获取 ref-clk 的位置。 在这两个选项中、 clk 环回都在我们的器件内部、如何 为外部 PHY 提供 RMII_MHz_50_CLK?

谢谢

肯

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好专家

当 AM2732配置为 RMII 模式时、我们需要将 RMII_MHz_50_CLK 输出到 CPSW 和 PHY。

我们可以使用 RMII_ref_clk_OE_n 来选择可获取 ref-clk 的位置。 在这两个选项中、 clk 环回都在我们的器件内部、如何 为外部 PHY 提供 RMII_MHz_50_CLK?

谢谢

肯

尊敬的 Ken:

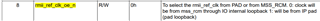

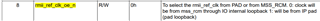

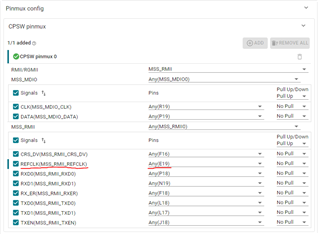

在 AM273 ZCE 封装中、焊球编号 E19 (焊盘名称 PADBX、焊球名称 RCSS_GPIO_49)可在多路复用器模式2中配置为输出 MSS_RMII_REFCLK。 请在 AM273数据表 99页的第20页中找到与此相关的更多详细信息。

也可以通过 SysConfig 工具配置相同的配置、如下图所示。

还请在 TMDS273GPEVM 中查找硬件实现详细信息、检查设计文件第28页中的原理图、其中 PHY 可以选择从 RCSS_GPIO_49 (多路复用器模式2上的 MSS_RMII_REFCLK)到 R341 (默认为 DNP/DNI 的0Ω Ω 电阻器)提供时钟。

请告诉我、这是否澄清了您的需求。

谢谢。

Tejas Kulakarni