主题中讨论的其他器件:ADS1605

与锁定螺纹相关:

请原谅这里的"新手"问题,但我暂时填补真正的处理器硬件和软件的人,我不是一个处理器家伙。

我需要将两个16位并行 ADC (ADS1605: https://www.ti.com/lit/ds/symlink/ads1605.pdf )连接到 ADS2434 R5 (AM2434BSDFIALVR、441引脚 ALV FCBGA),并在不使用 PRU 的情况下以1.25 MSPS (800 ns)的速率读取它们。

这似乎让 GPIO 保留为一个不错的选择,因为我们有很多备用的 GPIO 引脚,无法找到具有足够采样率/带宽和真正 SPI 输出与2434的本机 MCSPI 端口兼容的 delta-sigma ADC。 优先级很高的目标是接口没有 FPGA 或其他外部逻辑-我们需要使它在 ADC 和 CPU 之间是无缝的。

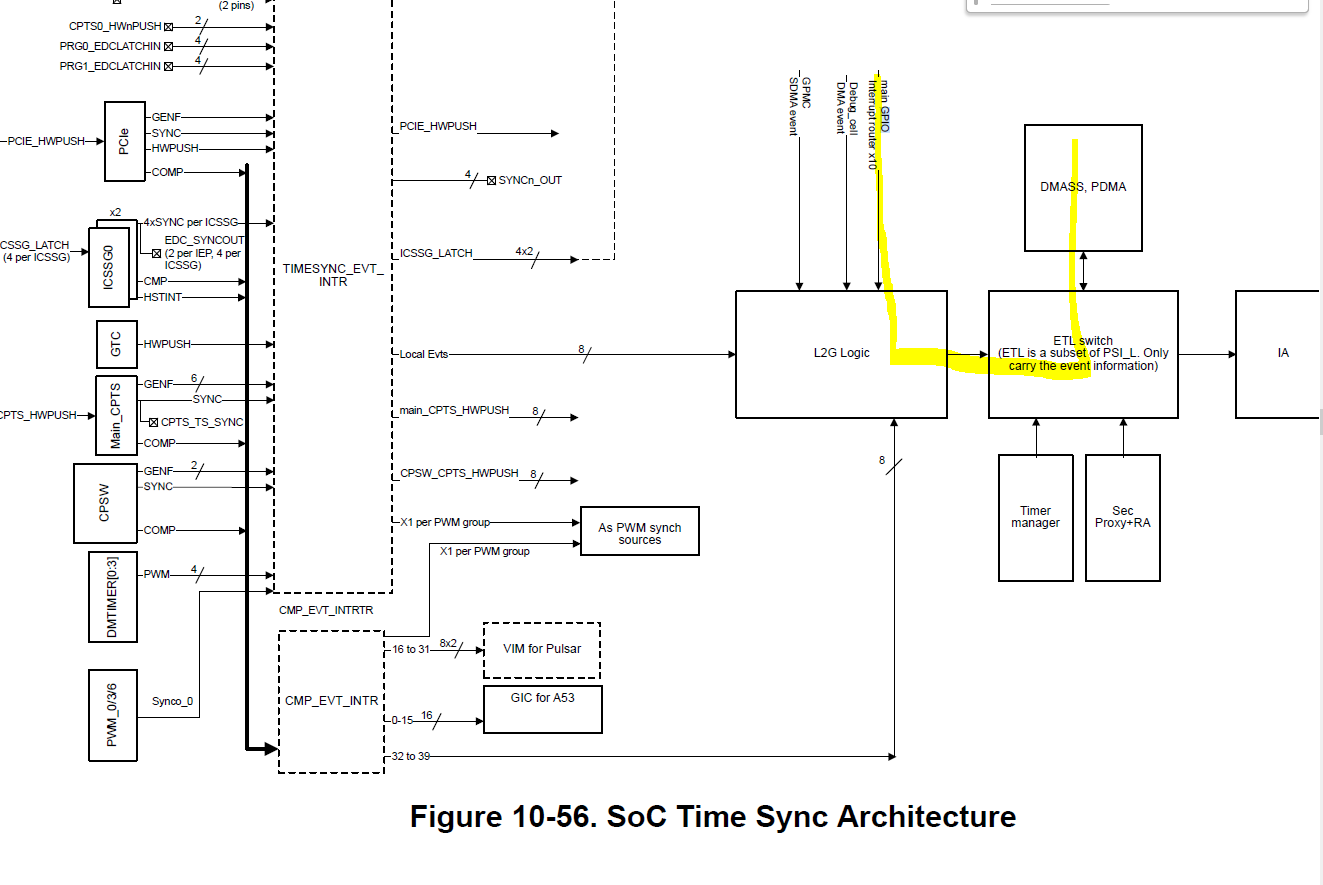

最大的问题是、2434能否通过硬件外设实现这些并行 ADC "自动"读取、以及通过 DMA 将样本写入缓冲区、而不会降低处理器的速度。

两个 ADS1605 ADC 将通过同一个外部低抖动采样振荡器运行、并通过 RESET 引脚进行同步、从而提供相干/同步采样。

当每个新样本准备就绪(每800ns 一次)时、DRDY 引脚将变为低电平、并且由于两个 ADC 同步、只需要一个 DRDY 信号作为 GPIO (中断?) 去抓取数据的输入。

2434上的 GPIO 看起来被分成16位的组。 由于我需要读取两个16位 ADC、如果这是作为一个32位读取来完成的、稍后在软件中将字分隔、但如果可以作为两个16位读取来完成、那也没关系。

作为增加的细微差别、我还想同时从每个 ADC 读取数据来读取超范围(OTR)引脚、但这会使每个输入进行17位读取(每个样本总计34位)。 我可以用 OTR 位替换每个 ADC 中的 LSB、并将输入数据视为15位 ADC、但这并不理想。

如果可以以32位的组形式读取输入、并且可以在每个 DRDY 脉冲上 DMA 两个流、则可以从每个 ADC 读取 ADC 数据为17位字(16数据+ 1 OTR、忽略其他15个)。

如果必须以16位为一组读取输入、则每个 DRDY 脉冲将进行三次读取:从第一个 ADC 读取16位、然后从第二个 ADC 读取16位、然后在第三次读取时忽略两个具有14位的 OTR 位。

大概 ADC CS 和 RD 引脚可以一直有效(低电平)、除了 CPU 在下一个 DRDY 下降沿之前读取这34个数据引脚所需的一切外、不需要进行位拆裂。

不过、数据流是可以实现的、我不能每隔800ns 就中断一次处理器来读取转换器。 在中断处理器或将处理器安排为处理帧之前、我需要从每个 ADC 采集4096个至4608个样本、才能通过 DMA 将这些样本存储在缓冲器中。

最好是在乒乓缓冲器之间进行交替存储。

在"缓冲区已满"状态(达到4096和4608之间的可编程结束限制)或定时器中断(周期=缓冲区大小*采样率)上"中断"处理器是可以接受的。

与我不是一个处理器的家伙和2434 TRM 超过10K 页... 我正在努力为这个架构提交一个板面布局布线而不做某些确认并行接口将工作在这个情况下。 使用 SPI 或 McBSP 时、这似乎都变得容易得多...

您可以对引脚/存储体分配(用于数据/OTR 状态)和引脚分配(GPIO、时钟、其他?)提供任何输入 那么总的来说、DRDY 脉冲以及外设配置(DMA、计时器、中断和 GPIO)和软件架构将会非常非常受欢迎。

非常感谢!