亲爱的香榭丽舍大街,

我是为我们的客户提出这个问题的。

用户知道 Cortex M0有多达32个 IRQx、并且有4个不同的优先级。

但对于组中断、用户关心的是如何调整其优先级。

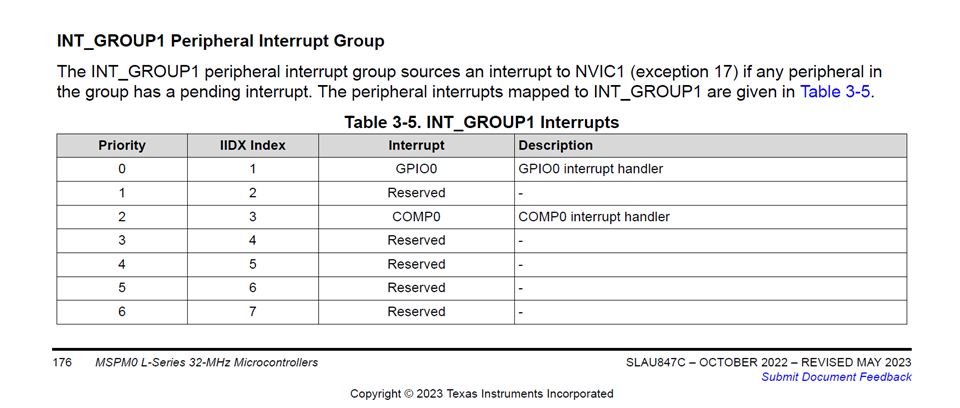

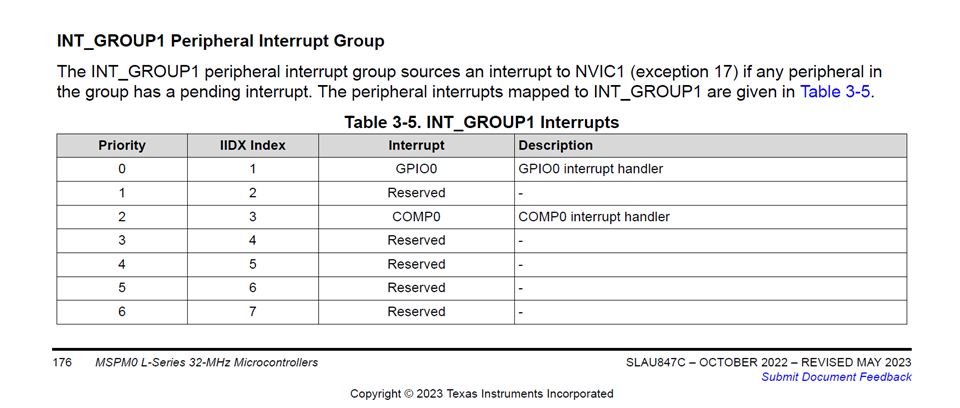

例如,如下面的组1,

是否可以使 COMP0的优先级低于 GPIO0?

2.是否可以使 COMP0的优先级低于 TIMG0、同时使 GPIO0的优先级高于 TIMG0?

3.是否可以使 COMP0的优先级高于 TIMG0、同时使 GPIO0低于 TIMG0?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

亲爱的香榭丽舍大街,

我是为我们的客户提出这个问题的。

用户知道 Cortex M0有多达32个 IRQx、并且有4个不同的优先级。

但对于组中断、用户关心的是如何调整其优先级。

例如,如下面的组1,

是否可以使 COMP0的优先级低于 GPIO0?

2.是否可以使 COMP0的优先级低于 TIMG0、同时使 GPIO0的优先级高于 TIMG0?

3.是否可以使 COMP0的优先级高于 TIMG0、同时使 GPIO0低于 TIMG0?

您好、 Wayne

您可以手动读取 COMP0和 GPIO0的 CPU_INT MIS 寄存器。

手动管理每个设置的中断、并通过写入 ICLR 寄存器手动清除中断标志。

在中断 IRQ 中逐个输入。

您可以首先读取 CPU_INT 寄存器的说明、包括 IIDX、IMASK、RIS、MIS、ISET、 ICLR.

在 TRM 的外设寄存器章节中。

https://www.ti.com/lit/pdf/slau847

8.3

此致、

赫利克