Other Parts Discussed in Thread: AM2631, AM2634

主题中讨论的其他器件: AM2634

鉴于 AM2631不支持 XIP (就地执行)、是否公平地假设完整的 SBL 和应用(从闪存到 QSPI)被传输到内部 RAM、因此内部 RAM 的数量是 两者的硬性限制(考虑到代码和数据)?

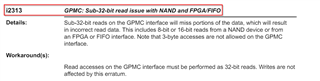

我们正在评估是否需要通过 GPMC 连接外部 RAM。 类似的传统系统将大约1MB 用于引导加载程序+ 2MB 应用程序、总共3MB 闪存和2MB RAM。

此致、

哈维尔