主题中讨论的其他器件:SysConfig

您好、TI 团队、

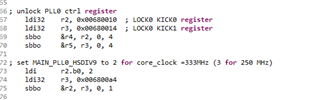

情况:在 am243 r5f-0-0内核中的 ICSSG1下运行 EtherCAT 固件、在 r5f-0-0内核中的 ICSSG0下运行 FSI 固件。 在 ICSSG0 PRU 中有一个如下的代码段:

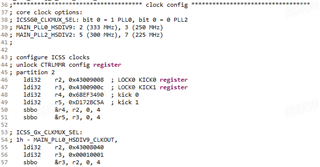

利用这些代码、运行 EtherCAT 的 ICSSG1的内核时钟只能配置为333333Hz、以便正常运行 EtherCAT、如下图所示。

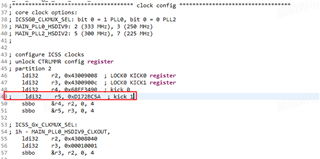

但如果 ICSSG0固件中的代码"ldi32 R5, 0xD172BC5A ; Kick 1"(如下图红色框中所示)被屏蔽。 运行 EtherCAT 的 ICSSG1的内核时钟可以配置为以其他频率运行、例如200000000Hz、并且 EtherCAT 仍然可以正常运行。

那么、为什么 ICSSG0中的这一句会影响 ICSSG1中的内核时钟配置呢? 这句'ldi32 r5、0xD172BC5A; kick 1 'play?

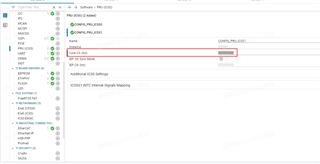

我还想知道哪个时钟源是运行 EtherCAT 固件的 ICSSG1的内核时钟? 它配置在哪里?

谢谢。