主题中讨论的其他器件: HALCOGEN

当我为该处理器编译演示时、page_functions.c 中有对未定义的测试寄存器 canREG1->test、mibspi1->PTESTEN、mibspi3->Eden 的引用。 这些在其他 TMS570处理器以及 RM42x、RM46x、RM48x 的演示中定义。 这些寄存器是否存在于 TMS570LC4357中、或者是否应排除这些测试?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

当我为该处理器编译演示时、page_functions.c 中有对未定义的测试寄存器 canREG1->test、mibspi1->PTESTEN、mibspi3->Eden 的引用。 这些在其他 TMS570处理器以及 RM42x、RM46x、RM48x 的演示中定义。 这些寄存器是否存在于 TMS570LC4357中、或者是否应排除这些测试?

Jagadish、

另外、在 HL_mibspi.h 中还缺少一整套针对 MIBSPI1的定义、这些定义是为 MIBSPI2、3、4、5定义的、例如 MIBSPI2_PAR_ECC_CTRL_CONFIGVALUE。 在 page_functions.c 中、没有针对 DCAN4_Parity 的代码、尽管其中有针对 DCAN1、2、3的代码。 第三、有针对 MIBSPI1_Parity 和 MINSPI3_Parity 和 MIBSPI5_Parity 的代码、但是针对 MIBSPI2和 MIBSPI4的代码没有。 如果我必须修改 SafeTI 代码、这似乎会违背 使用预定义的 SafeTI 库的目的。

尊敬的 Darryl:

也缺失 HL_mibspi.h 中为 MIBSPI1定义的一整套定义,这些定义是为 MIBSPI2、3、4、5定义的,例如 MIBSPI2_PAR_ECC_CTRL_CONFIGVALUE。

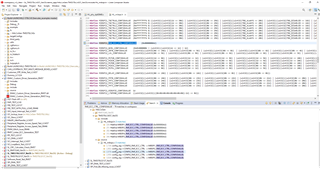

它在那里、对吧? 查看以下 pic:

和在 page_functions.c 中没有针对 DCAN4_Parity 的代码,尽管有针对 DCAN1、2、3的代码。 第三、有针对 MIBSPI1_Parity 和 MINSPI3_Parity 和 MIBSPI5_Parity 的代码、但是针对 MIBSPI2和 MIBSPI4的代码没有。 如果我必须修改 SafeTI 代码、这似乎背离了 使用预定义的 SafeTI 库的目的。

我找不到、能否提供屏幕截图以便更好地理解。

--

谢谢。此致、

Jagdish。

coreEnableFlashEcc ()和 coreDisableFlashEcc ()存在于其他处理器的 hl_sys_core.asm 中、但不存在于 TMS570LC43x 分支中。 我没有找到导致生成它们的 HALCoGen 设置。

程序闪存的 ECC 逻辑 在复位时启用、并且不能被禁用。

很难提供缺失内容的屏幕截图。 以下是错误

这是 HALCoGen/TMS570LC43x/include/HL_reg_mibspi.h 中的定义。

[/报价]PTESTEN 和 Eden 是 PAR_ECC_CTRL 寄存器的两个位字段。 在 HalCoGen 代码和 SDL API 中、我们将寄存器定义为32位寄存器、并且不会将其细分为位字段结构。

和在 page_functions.c 中没有针对 DCAN4_Parity 的代码,尽管有针对 DCAN1、2、3的代码。 第三、有针对 MIBSPI1_Parity 和 MINSPI3_Parity 和 MIBSPI5_Parity 的代码、但是针对 MIBSPI2和 MIBSPI4的代码没有。 如果我必须修改 SafeTI 代码、这似乎背离了 使用预定义的 SafeTI 库的目的。

HalCoGen 不会为 TMS570LC43x 器件生成这些文件。 您可以使用 SDL 执行 MibSPI 和 DCAN RAM ECC 自检。

例如:

Test_Mib 45C(MIBSPI_ECC_TEST_MODE_1bit, SL_MIBSPI4);

SL_SelfTest_CAN (CAN_ECC_TEST_MODE_1bit_FAULT_Inject、SL_DCAN4);

在 TMS570LC43x 的演示代码中,在 flash.c 中, ATCM Correctable_Error ()函数引用 coreDisableFlashECC ()和 coreEnableFlashECC ();。

C:\ti\Hercules\Hercules Safety MCU Demos\4.0.0\TMS570LC43x_target_sources\demo-app\source\flash.c

这不是我的 TMS570LC4357的正确演示代码吗?

感谢您指出这一点。

ATCM (void)不能用于 Correctable_Error 和 TMS570LC43x。 这两个器件是基于 Cortex-R5F 的 ARM MCU、而所有其他器件是基于 Cortex-R4F 的器件。 可以启用/禁用 Cortex-R4F 器件上闪存的 ECC 逻辑、并且可以手动写入 ECC 空间(用于错误注入)。 但对于 Cortex-R5F、我们使用不同的方法来注入 ECC 错误。

请使用安全诊断库、而不是 dmeo 示例。