您好!

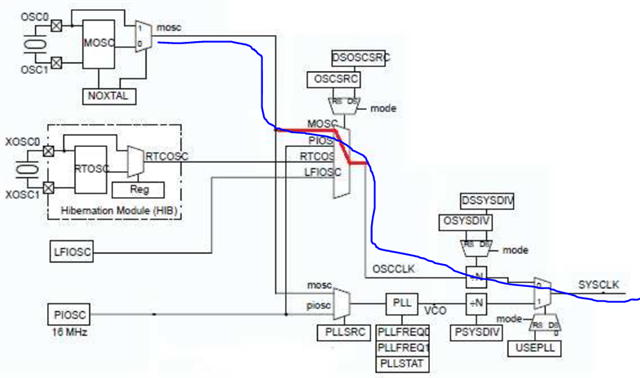

我的客户希望使用20MHz MOSC 时钟作为 SYSCLK 源。 SYSCLK 也是20MHz。

两个时钟(MOSC 和 SYSCLK)的时钟相位必须对齐。

客户希望将 MOSC 用作 PLL 旁路的 SYSCLK 源、但勘误表 SYSCTL#23指出它可能会导致"复位时出现总线故障"。

问题#1:

客户通过以上用例测试、工作正常、没有任何问题。

这里的"总线故障"究竟意味着什么?

是否有任何其他情况会导致总线故障?

问题2:

假设 PLL 用作 MOSC 作为 PLL 源、则将时钟乘以 N 并除以 N、SYSCLK 频率配置为20MHz。

这可以用作权变措施、但在本例中、MOSC 和 SYSCLK 的时钟相位仍然对齐?

客户担心存在 N 个不同的相位组合。

谢谢。此致、

田代浩一郎