您好、专家!

因此、我想实施一个多内核项目以同时使用 CPSW 和 ICSSG LWIP 堆栈。 动机如下:

- 内核 r5Fss0-0:实施示例 "enet_lwip_cpsw"、源: enet_lwip_cpsw (TI.com) @ AM243x 的 MCU+ SDK (09.00.00.35)

- 内核 r5Fss0-1:实现函数 "enet_lwip_icssg"、源 enet_lwip_icssg (TI.com) @用于 AM243x 的工业通信 SDK (09.00.00.03)

我阅读了 SDK 文档、了解 如果要对多个内核进行操作、则需要分配资源和更改链接器命令。 我已经在系统配置和链接器脚本中进行了必要的更改。

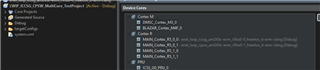

因此、我创建了一个 CCS 的"系统"工程、 如下所示:

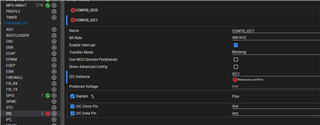

这里需要注意的是、两个示例分别在两个所需的内核上运行、但当我尝试编译/编译组合的多内核工程时、我收到错误消息说两个内核之间存在资源冲突、如下面的片段所示:

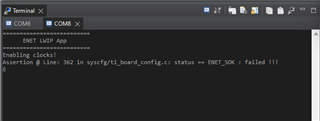

我尝试为 I2C_2和 I2C_3等其他 I2C 实例以及 MCU 域实例分配、这种更改使构建成功、但在运行时、基于 CPSW 的应用程序无法从 EEPROM 读取 MAC 地址、并且我收到以下断言故障:

另外、根据用户指南、可以看出 I2C0和 I2C1是正确的实例:/resized-image/__size/320x240/__key/communityserver-discussions-components-files/908/pastedimage1699372110278v1.png

我缺少什么? 是否需要遵循不同的方法。 是否需要进行一些驱动程序更改?

请告知。

非常感谢、此致、

肖巴赫特