主题中讨论的其他器件:HALCOGEN

您好!

在调用 systemInit()例程(由 Halcogen 创建)之前,即在配置 PLL 和时钟之前,时钟值是什么?

是否可以在 systemInit()之前启用看门狗? 如果是、RTICLK1的值是多少? 是否需要在 systemInit()后重新配置看门狗?

此致、

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Marcio:

复位后、器件默认为 OSCIN 上的时钟、这意味着它将直接使用晶体频率运行。

Unknown 说:是否可以在 systemInit()之前启用看门狗? 如果是、RTICLK1的值是多少? 是否需要在 systemInit()后重新配置看门狗?

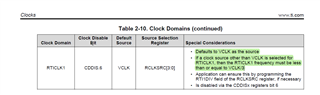

可以为 RTICLK1选择不同的时钟源并且我们甚至可以为 RTICLK 选择 OSC 时钟。

因此、根据这一点、它应该也在 PLL 之前起作用。

但是、有一个条件需要满足、

如果 RTI 的时钟源是其他 VCLK、则 RTI 频率必须小于 VCLK/3。 请确保执行该操作。

这只是理论、但请尝试在实践中进行测试。

--

谢谢。此致、

Jagadish。

您好 Jagadish:

感谢您的答复。

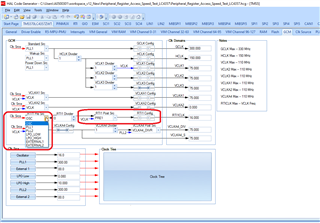

我的程序做得不对。 它在调用 errata_SSWF021_45_both_plls ()和 mapClocks ()之前配置看门狗。 如果我没有弄错、 请查看 RTI 时钟源寄存器(RCLKSRC) 、此时 RTICLK 等于 VCLK、这不符合 VCLK/3规则。

根据观察, 在调用 errata_SSWF021_45_both_PLLs()之前将看门狗纹波配置为128ms 不起作用。 但将 Texp 设置为256ms 可以正常工作。

VCLK 是否在复位静态75MHz 之后?

此致、

Marcio。

尊敬的 Marcio:

重置后 VCLK 是否是75MHz?

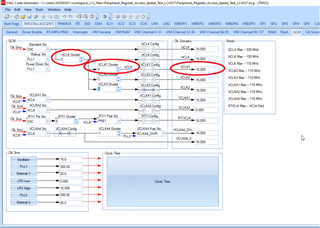

根据 TRM、复位后、时钟源0是 GCLK1、HCLK、VCLK 的源。

这意味着这是 OSCIN:

它们对应的分频器也默认为零。

因此、据我了解、在初始化之前、VCLK 频率也等于振荡器频率、即 e.16MHz。

--

谢谢。此致、

Jagadish。