大家好、

我的客户正在考虑将 TM4C1299NCZAD 与我们的新设计电路板一起使用。

他们正在考虑将 TM4C1299NCZAD 用于新的设计电路板。

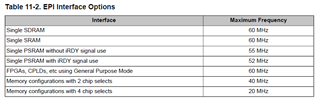

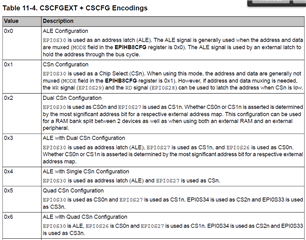

他们正在研究是否可以使用 EPI 或 Quad-SSI 连接 TI 微控制器与 FPGA 之间的通信接口、从而控制存储器映射。

■问题

1) 1)使用 Quad-SSI 可以实现存储器映射控制吗?

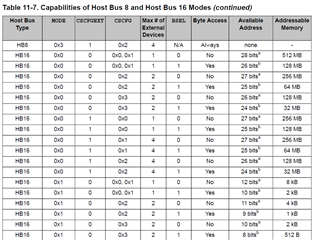

2) 2) 根据数据表、似乎 EPI 可以设置8/16/32位并行总线。

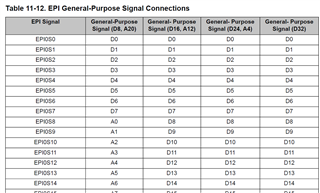

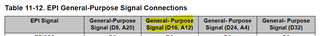

用于 EPI 8位、16位和32位的 IO 数量是多少? (抱歉、我查看了数据表、但我真的不明白如何阅读。)

通信格式和 IO 数量将根据 SDRAM 和 SRAM 等选项设置而变化、

但他们正在考虑使用 EPI 8位来在提供高速访问的同时减少 IO 的数量。