主题中讨论的其他器件:MSP432E401Y

大家好!

我在 MSP432P4系列器件(MSP432P401R)上运行了现有软件。 由于 MSP432P4系列已停产、我希望将该软件迁移到 MSP432E4系列器件(MSP432E401Y)、直到找到更持久的解决方案、并重新设计该软件。

由于现有软件是使用 TI 驱动程序编写的、因此我的理解是从 MSP432P4系列器件更改为 MSP432E4系列器件应相当简单(从软件角度而言)。

现有软件基于 MSP432P401R 的可移植 TI 驱动程序 FreeRTOS 示例项目(C:\ti\simplelink_msp432p4_SDK_3_40_00_05\examples\rtos\MSP_EXP432P401R\demos\portable\freertos\ccs\portable_MSP_EXP432P401R_freertos_ccs.projectspec)。 迁移的软件基于 MSP432E401Y 的可移植 TI-Drivers FreeRTOS 示例项目(C:\ti\simplelink_msp432e4_SDK_4_20_00_12\examples\rtos\MSP_EXP432E401Y\demos\portable\freertos\ccs\portable_MSP_EXP432E401Y_freertos_ccs.projectspec)。

我已经开始从引脚排列/外设兼容性开始调查此迁移是否可行。

现有软件使用大约24个 GPIO、4个 UART 接口、2个 I2C 接口、1个 SPI 接口和6个 ADC 输入。 MSP432E401Y 在外设方面兼容:有足够的 GPIO、UART、I2C、SPI 和 ADC 接口。

但是、在使用外部48 MHz 时钟源时、我遇到了难题。

现有软件依赖于外部单端48 MHz 时钟源。 在 MSP432P401R 上、TI 驱动程序电源模块提供了创建自定义性能级别并通过 PowerMSP432_ConfigV1结构配置外部时钟的选项。 我无法为 MSP432E401Y 找到此类选项。 我的印象是、使用 TI 驱动器不容易实现此类连接。

为确保脚潮湿、我查阅了数据表(DTS)和技术参考手册(TRM)、了解详情。

[0.] 根据[TRM:4.1.5.1基本时钟源]:"PIOSC 是 POR 期间和之后微控制器使用的片上时钟源。"

[1.] 根据[TRM:4.1.5.1基本时钟源]:"MOSC 提供一个频率精确的时钟、时钟源由两种方式之一提供:外部单端时钟源连接到 OSC0输入管脚、或外部晶振连接到 OSC0输入管脚和 OSC1输出管脚。 单端时钟源的范围从直流到微控制器指定的速度。"

[2.] 根据[DTS: Table 5-12. 主振荡器输入特性]:"外部时钟基准(PLL 处于旁路模式)"(f_REF_XTAL_BYPASS)的最小值和最大值分别为0 MHz 和120 MHz。

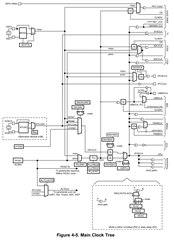

[3.] 根据[TRM: Figure 4-5. 主时钟树]:"mosc"时钟信号来自一个多路复用器、其输入由控制信号"NOXTAL"选择。

[4.] 根据[ TRM:表4-20. MOSCCTL 寄存器字段描述]:PWRDN 寄存器位字段。。 "提供用户对主振荡器电路断电的控制。 当使用晶振且设置为单端模式时、该位应该被清零... 0x0 =启用 MOSC 电源电路。 0x1 = MOSC 电路断电。'

[5.] 根据[ TRM:表4-20. MOSCCTL 寄存器字段说明]:NOXTAL 寄存器位字段…… "为用户提供对从主控制器

振荡器电路。 当使用晶体或单端模式时、该位应置位。 如果应用程序需要 MOSC、则应将此位清零。'

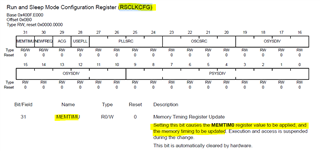

[6.] 根据[ TRM:表4-21. RSCLKCFG 寄存器字段说明]:USEPLL 寄存器位字段... "控制时钟源是由 OSCSRC 域指定、还是 PLL 的输出提供给系统时钟分频器并用作系统时钟源。 0x0 =时钟源由 OSCSRC 域指定。 0x1 =时钟源由 PLL 指定。"

[7.] 根据[ TRM:表4-21. RSCLKCFG 寄存器字段描述]:OSCSRC 寄存器的位字段"指定成为振荡器时钟(OSCCLK)源的振荡器源、在 RUN 或 SLEEP 模式期间绕过 PLL 时使用它... 0x3 = MOSC 是振荡器源。"

[8.] 根据[表4-26. DSCLKCFG 寄存器字段描述]:DSOSCSRC 寄存器的位字段"指定成为振荡器时钟(OSCCLK)源的振荡器源、在深度睡眠模式绕过 PLL 时使用它... 0x3 = MOSC"

根据[1、2]、可以看到 MSP432E401Y 可以支持频率为48 MHz 的单端外部时钟参考。

根据[0、3、4、5、6、7、8]、可能会显示、忽略 OSCCLK 时钟分频器(我期望默认为1)、如果我要使 SYSCLK 成为以我的单端外部时钟作为源的48 MHz 时钟、我应该:

[A.]设置 MOSCCTL。 自动断电

[B]清除 MOSCCTL。 NOXTAL

[c.]清除 RSCLKCFG。 USEPLL

[D.]将0x3分配给 RSCLKCFG。 DSOSCSRC

[E.]将0x3分配给 RSCLKCFG。 OSCSRC

你认为这会起作用吗? 如果没有、我接下来可以从哪里寻找解决方案?

最终、我可以设计一个原型板并使用实际外部时钟对此进行测试、但在执行此操作之前、我想详细列出所有其他选项。

非常感谢、

迪伦

时钟树、参考: