您好!

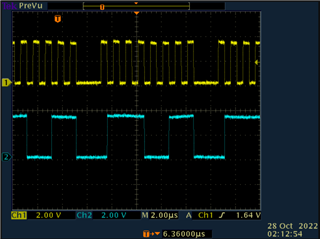

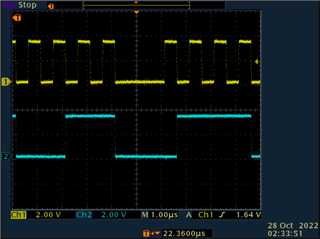

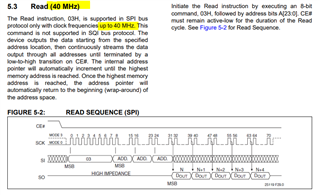

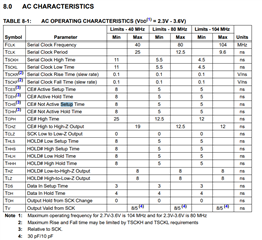

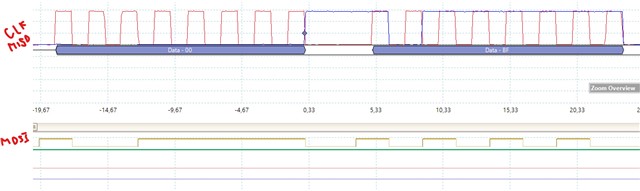

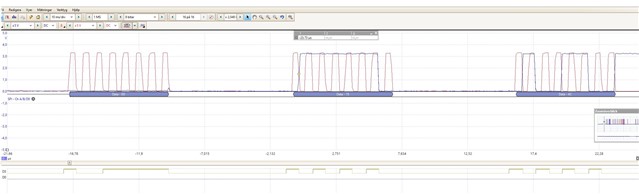

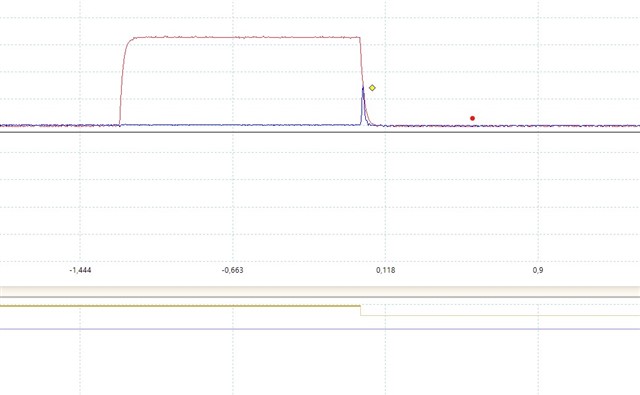

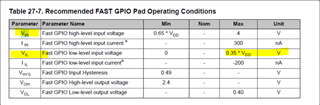

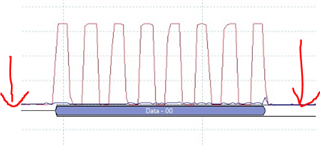

我们将 SS2用作 SPI、并尝试从外部闪存配置、写入和读取数据。 一切都运行正常、但有时我们从闪存芯片读取了 MISO 上的错误数据。 例如、如果我们预期01 02 03 04 05 06、则可以是所有数据都是00、也可以是一些随机数。

我们曾尝试切换到 SS3、但同样的问题仍然存在。 我们已经验证时钟信号是正确的、并且 MOSI 上的数据是正确的、但是闪存芯片没有响应我们的偶尔要求。 是否闪存芯片与 CPU 不兼容? 我们使用另一个系列的闪存 SST26VF064B。

提前感谢您!

此致、

格尔加纳

。

。