主题中讨论的其他器件:HALCOGEN

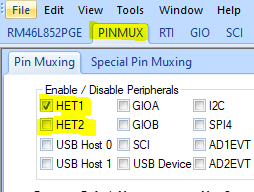

我在通过 N2HET 配置 DMA REQ 时遇到问题。

我的 HET 代码会生成一个 PWM、当比较匹配项 DE PWM 上升时、生成 DE 请求。 我试图将数据重定向到 HET1的前8个引脚、似乎无法分辨。

有人能帮忙吗?

这是 带有来自 HalCoGen 的所有驱动程序的主代码。

非常感谢、

尼诺·奥利弗

/** @file sys_main.c

* @brief Application main file

* @date 11-Dec-2018

* @version 04.07.01

*

* This file contains an empty main function,

* which can be used for the application.

*/

/*

* Copyright (C) 2009-2018 Texas Instruments Incorporated - www.ti.com

*

*

* Redistribution and use in source and binary forms, with or without

* modification, are permitted provided that the following conditions

* are met:

*

* Redistributions of source code must retain the above copyright

* notice, this list of conditions and the following disclaimer.

*

* Redistributions in binary form must reproduce the above copyright

* notice, this list of conditions and the following disclaimer in the

* documentation and/or other materials provided with the

* distribution.

*

* Neither the name of Texas Instruments Incorporated nor the names of

* its contributors may be used to endorse or promote products derived

* from this software without specific prior written permission.

*

* THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

* "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

* LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

* A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT

* OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL,

* SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT

* LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

* DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY

* THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT

* (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

* OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

*

*/

/* USER CODE BEGIN (0) */

#include "het.h"

#include "mibspi.h"

#include "sys_dma.h"

#include "gio.h"

#include "PWM.h"

/* USER CODE END */

/* Include Files */

#include "sys_common.h"

/* USER CODE BEGIN (1) */

/* USER CODE END */

/** @fn void main(void)

* @brief Application main function

* @note This function is empty by default.

*

* This function is called after startup.

* The user can use this function to implement the application.

*/

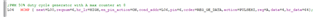

/* USER CODE BEGIN (2) */

#define D_SIZE 2

void dmaConfigCtrlPacket(uint32 sadd,uint32 dadd,uint32 dsize);

void mibspiDmaConfig(mibspiBASE_t *mibspi,uint32 channel, uint32 txchannel, uint32 rxchannel);

uint8 TX_DATA[D_SIZE] = {1<<6,0x0} ; /* transmit buffer in sys ram */

static uint8 *reg_out; //output register

g_dmaCTRL g_dmaCTRLPKT; /* dma control packet configuration stack */

/* USER CODE END */

uint8 emacAddress[6U] = {0xFFU, 0xFFU, 0xFFU, 0xFFU, 0xFFU, 0xFFU};

uint32 emacPhyAddress = 0U;

int main(void)

{

/* USER CODE BEGIN (3) */

hetInit();

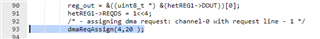

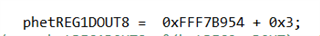

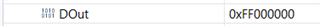

reg_out = &((uint8_t *) &(hetREG1->DOUT))[0];

hetREG1->REQDS = 1<<4;

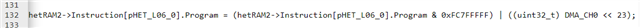

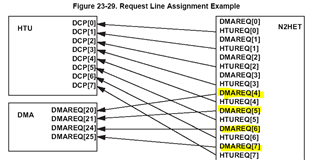

/* - assigning dma request: channel-0 with request line - 1 */

dmaReqAssign(4,20 );

/* - configuring dma control packets */

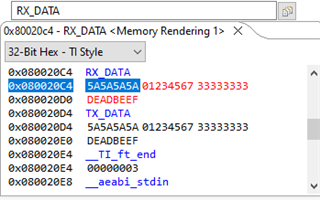

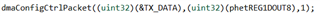

dmaConfigCtrlPacket((uint32)(&TX_DATA),(uint32)reg_out,D_SIZE);

/* upto 32 control packets are supported. */

/* - setting dma control packets */

dmaSetCtrlPacket(DMA_CH4,g_dmaCTRLPKT);

/* - setting the dma channel to trigger on h/w request */

dmaSetChEnable(DMA_CH4, DMA_HW);

/* - enabling dma module */

dmaEnable();

while(1)

{

}

/* USER CODE END */

}

/* USER CODE BEGIN (4) */

/** void dmaConfigCtrlPacket(uint32 sadd,uint32 dadd,uint32 dsize)

*

* configuring dma control packet stack

*

* sadd > source address

* dadd > destination address

* dsize > data size

*

* @ note : after configuring the stack the control packet needs to be set by calling dmaSetCtrlPacket()

*/

void dmaConfigCtrlPacket(uint32 sadd,uint32 dadd,uint32 dsize)

{

g_dmaCTRLPKT.SADD = sadd; /* source address */

g_dmaCTRLPKT.DADD = dadd; /* destination address */

g_dmaCTRLPKT.CHCTRL = 0; /* channel control */

g_dmaCTRLPKT.FRCNT = 1; /* frame count */

g_dmaCTRLPKT.ELCNT = dsize; /* element count */

g_dmaCTRLPKT.ELDOFFSET = 4; /* element destination offset */

g_dmaCTRLPKT.ELSOFFSET = 0; /* element destination offset */

g_dmaCTRLPKT.FRDOFFSET = 0; /* frame destination offset */

g_dmaCTRLPKT.FRSOFFSET = 0; /* frame destination offset */

g_dmaCTRLPKT.PORTASGN = 4; /* port b */

g_dmaCTRLPKT.RDSIZE = ACCESS_16_BIT; /* read size */

g_dmaCTRLPKT.WRSIZE = ACCESS_16_BIT; /* write size */

g_dmaCTRLPKT.TTYPE = FRAME_TRANSFER ; /* transfer type */

g_dmaCTRLPKT.ADDMODERD = ADDR_INC1; /* address mode read */

g_dmaCTRLPKT.ADDMODEWR = ADDR_OFFSET; /* address mode write */

g_dmaCTRLPKT.AUTOINIT = AUTOINIT_ON; /* autoinit */

}

/* USER CODE END */

IRA