大家好、

我是 FAE Jayden、我的客户 O-net 使用 AM2434、他们对这款插槽有一些疑问。

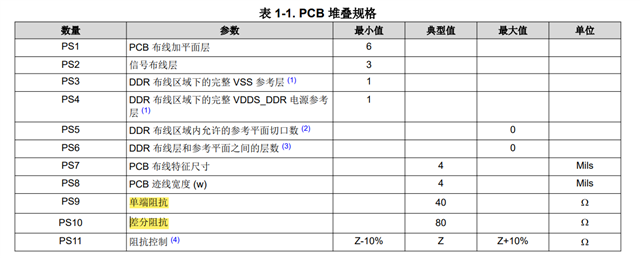

对于 DDR4设计、有关于 AM2434 DDR4 PCB 设计的 APN: AM64x/AM243x DDR 电路板设计和布局指南(修订版 A)(在 APN 中为 ti.com.cn);)、建议的典型 PCB 单端阻抗和差分阻抗为80Ω。 如果按照传统的50/LVDS 设计100Ω、是否会影响信号质量? 40/DDR4 80Ω 阻抗还能满足市场上大多数 DDR4芯片的要求吗?

2. AM2434的 PCIe RX/TX PCB 单端阻抗和差分阻抗的建议值是多少? 下图展示了 On-Net 对 PCIe 的设计、没问题吧?

3. AM2434对耦合电容器的材料有任何要求吗?

谢谢

BRS

杰登