Other Parts Discussed in Thread: HALCOGEN, RM57L843

主题中讨论的其他器件:HALCOGEN、

大家好、团队成员。

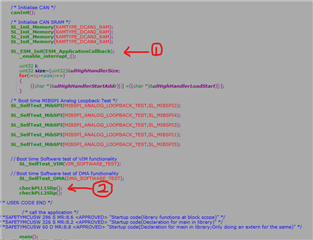

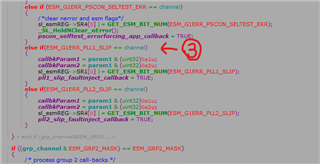

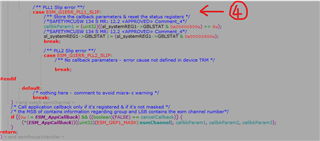

根据安全手册(SPNU575A)、我采用了 PLL1转差检测器(CLK2)。

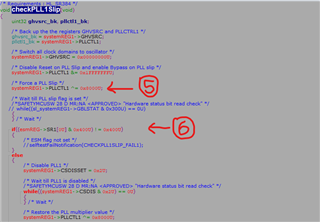

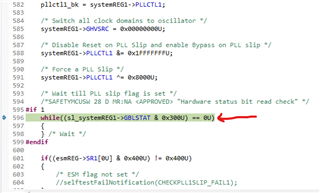

我复制了 demo_app (..\SafeTI Diagnostic Library\2.4.0\demo_app\common\source\faultInject.c)中 TI 样例代码的 checkPLL1Slip () checkPLL2Slip ()。

然而,系统会在 checkPLL1Slip()中停止。

CheckPLL2Slip()没有问题。

这是我的 setupPLL()代码。

void setupPLL(void)

{

/* USER CODE BEGIN (3) */

/* USER CODE END */

/* Disable PLL1 and PLL2 */

systemREG1->CSDISSET = 0x00000002U | 0x00000040U;

/*SAFETYMCUSW 28 D MR:NA <APPROVED> "Hardware status bit read check" */

while((systemREG1->CSDIS & 0x42U) != 0x42U)

{

/* Wait */

}

/* Clear Global Status Register */

systemREG1->GBLSTAT = 0x301U;

/** - Configure PLL control registers */

/** @b Initialize @b Pll1: */

/** - Setup pll control register 1:

* - Setup reset on oscillator slip

* - Setup bypass on pll slip

* - setup Pll output clock divider to max before Lock

* - Setup reset on oscillator fail

* - Setup reference clock divider

* - Setup Pll multiplier

*/

systemREG1->PLLCTL1 = (uint32)0x00000000U

| (uint32)0x20000000U

| (uint32)((uint32)0x1FU << 24U)

| (uint32)0x00000000U

| (uint32)((uint32)(8U - 1U)<< 16U)

| (uint32)(0xA400U);

/** - Setup pll control register 2

* - Setup spreading rate

* - Setup bandwidth adjustment

* - Setup internal Pll output divider

* - Setup spreading amount

*/

systemREG1->PLLCTL2 = (uint32)((uint32)255U << 22U)

| (uint32)((uint32)7U << 12U)

| (uint32)((uint32)(1U - 1U) << 9U)

| (uint32)61U;

/** @b Initialize @b Pll2: */

/** - Setup pll2 control register :

* - setup Pll output clock divider to max before Lock

* - Setup reference clock divider

* - Setup internal Pll output divider

* - Setup Pll multiplier

*/

systemREG2->PLLCTL3 = (uint32)((uint32)(1U - 1U) << 29U)

| (uint32)((uint32)0x1FU << 24U)

| (uint32)((uint32)(8U - 1U)<< 16U)

| (uint32)(0xA400U);

/** - Enable PLL(s) to start up or Lock */

systemREG1->CSDIS = 0x00000000U

| 0x00000000U

| 0x00000008U

| 0x00000080U

| 0x00000000U

| 0x00000000U

| 0x00000000U

| 0x00000004U;

}

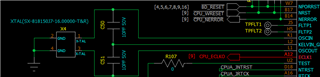

我的 电路板是定制电路板。 (非评估板)

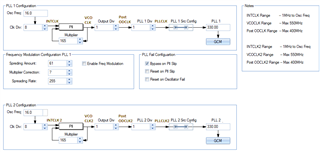

下面是 Halcogen 中的 PLL 设置。

请让我知道哪里错了。

祝你一切

顺利。 基因。