尊敬的 TI 专家:

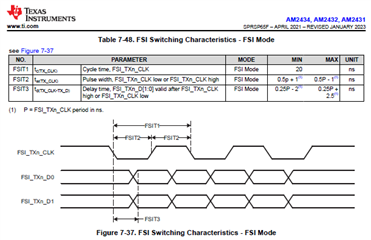

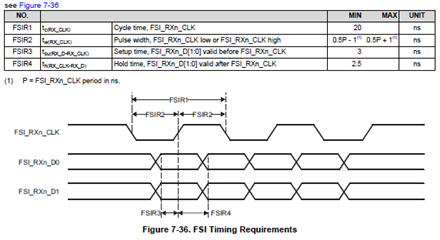

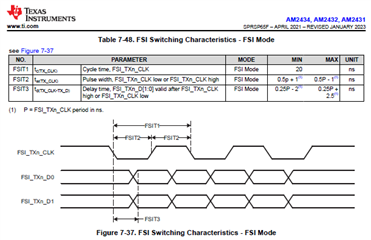

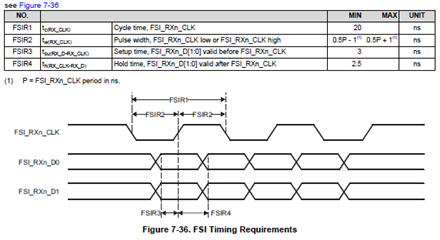

当 FSI_CLK = 50MHz = 20ns、Tsu_min (3ns)时 、为 大于 [TW_rxclk_min (0.5*20 - 1=9)-td_max (0.25*20+2.5=7.5)= 1.5ns]、根据如下所示的值。

您能告诉我、我们的计算是否存在任何问题吗?

非常感谢!

Kevin

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 TI 专家:

当 FSI_CLK = 50MHz = 20ns、Tsu_min (3ns)时 、为 大于 [TW_rxclk_min (0.5*20 - 1=9)-td_max (0.25*20+2.5=7.5)= 1.5ns]、根据如下所示的值。

您能告诉我、我们的计算是否存在任何问题吗?

非常感谢!

Kevin

Kevin 老师、您好!

请参阅我收到的以下输入

[报价 userid="546457" url="~/support/microcontrollers/arm-based-microcontrollers-group/arm-based-microcontrollers/f/arm-based-microcontrollers-forum/1364179/am2432-fsi-clk-50mhz-not-match-time-series-requirement/5209466 #5209466"]此用例如下所示。 两个 AM243x 使用 FSI 传输数据。

时钟频率为50MHz、传输速度为100MHz。

[报价]在这种情况下、客户需要在考虑 AM64x 开关特性、AM64x 时序要求及其实际 PCB 电路板布线延迟的情况下执行时序分析、以确定允许的最大工作频率、从而为最小建立/保持要求提供足够的裕度。

此致、

Sreenivasa

Kevin 老师、您好!

谢谢你。

如果客户使用的是 TDA4 + AM24、此处的 AM64x 还可以参考 TDA4?

请详细说明问题。

问题是 AM64x 是否可以替换为 TDA4、我怀疑 TDA4是否有 FSI 接口。

https://www.ti.com/lit/ds/symlink/tda4vm.pdf

此致、

Sreenivasa

尊敬的 Sreenivasa:

我已从客户处确认、我们误解了这个问题。 问题是在 AM24x 自传输和自接收的条件下、当 FSI CLK 为50MHz 时、是否可能存在时间串行问题。 客户不同意我们之前的说明、因为他们认为此问题与主器件 AM64x 或 TDA4x 没有关系。

提出这个问题的原因来自我们可以在下面计算的数据表。

Tsu_min (3ns) 为 大于 [TW_rxclk_min (0.5*20 - 1=9)-td_max (0.25*20+2.5=7.5)= 1.5ns]

您能不能帮忙检查这一点吗?如果我们的计算有误、还请指出这一点。

谢谢!

Kevin

Kevin 老师、您好!

仅供参考、软件应用团队在下面创建了几个常见问题解答。

此致、

Sreenivasa