工具与软件:

您好!

我正在使用安全诊断库(SDL)和 SDL 演示例实现针对闪存和 SRAM 的2位 ECC 测试。

但我在这些测试中遇到失败、并且很难确定原因。

retVal = SL_SelfTest_SRAM(SRAM_ECC_ERROR_FORCING_2BIT, TRUE, &failInfoTCMRAM); INCREMENT_PASS_FAIL_COUNTER(failInfoTCMRAM, retVal); // failInfoTCMRAM = ST_FAIL /* Run 2Bit ECC test on Flash */ retVal = SL_SelfTest_Flash(FLASH_ECC_TEST_MODE_2BIT, TRUE, &failInfoFlash); INCREMENT_PASS_FAIL_COUNTER(failInfoFlash, retVal); // failInfoFlash = ST_FAIL

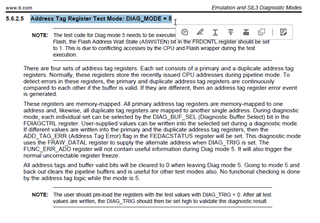

此外、我注意到、在 SDL 演示示例中、某个测试在sys_startup.c文件中被注释掉。 有人能解释一下为什么对这个测试进行评论吗?

默认情况下是否存在禁用它的特定原因或条件?

#if 0 /* Run Address tag mode test on Flash */ retVal = SL_SelfTest_Flash(FLASH_ECC_ADDR_TAG_REG_MODE, TRUE, &failInfoFlash); INCREMENT_PASS_FAIL_COUNTER(failInfoFlash, retVal); #endif

谢谢、此致、

Ilija