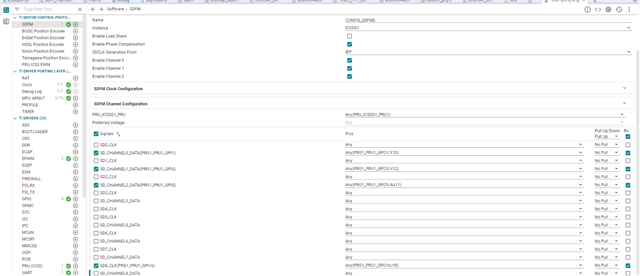

主题中讨论的其他器件:SysConfig

工具与软件:

您好!

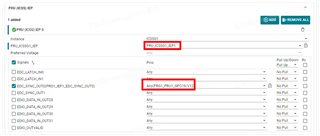

我尝试使用基于 motor control SDK 的 single_chip_servo_am243x-lp_r5fss0-0_nortos 的 SDDF。

在本示例中、SDDF 为 ICSSG0和 PRU0。 我的电路板上是 ICSSG1 PRU1、芯片是 AM2431-ALV。

问题在于 gSddfChSamps 保持为0、rtuSddfIrqHandler 在初始化后绝不会触发。

修改如下、

1. MCLK_IEP_SYNC.c

e2e.ti.com/.../mclk_5F00_iep_5F00_sync.c

在该文件中、所有 CSL_PRU_ICSSG0_IPE0_BASE 都更改为 CSL_PRU_ICSSG1_IEP1_BASE。

// Set SYNC0/1 high pulse time in iep clok cycles ( 7 clocks for 20 MHz at 300 MHz iep clk)

//HW_WR_REG32(USED_IEP_BASE+CSL_ICSS_G_PR1_IEP0_SLV_SYNC_PWIDTH_REG, 0x0006);

// Set SYNC0/1 high pulse time in iep clok cycles ( 5 clocks for 20 MHz at 200 MHz iep clk)

HW_WR_REG32(USED_IEP_BASE+CSL_ICSS_G_PR1_IEP0_SLV_SYNC_PWIDTH_REG, 0x0004);

// Set SYNC0/1 period ( 15 clocks for 20 MHz at 300 MHz iep clk)

//HW_WR_REG32(USED_IEP_BASE+CSL_ICSS_G_PR1_IEP0_SLV_SYNC0_PERIOD_REG, 14);

// Set SYNC0/1 period ( 10 clocks for 20 MHz at 300 MHz iep clk)

HW_WR_REG32(USED_IEP_BASE+CSL_ICSS_G_PR1_IEP0_SLV_SYNC0_PERIOD_REG, 9);

时钟也会更新、因为基本时钟和 IEP 时钟更改为200MHz。 PRG1_PRU1_PGI16 (V12)可以成功输出20Mhz 时钟。

2. sddf.c

在该文件函数 initSddf 中、

对于基于200MHz 时钟的20Mhz 输出、ECAP_DIVIDER 的默认值更改为9。

pruicssIep 更改为 IEP1

hSdfm->pruicssIep =(void *)(((PRUICSS_HwAttrs *)(pruIcssHandle->hwAttrs)->iep1RegBase);

3. single_chip_servo.c.

e2e.ti.com/.../single_5F00_chip_5F00_servo.c

在该文件中、我删除了所有 endat 相关代码。

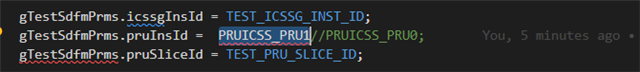

ICSSG 和 PRU 更改为 ICSSG1 PRU1。

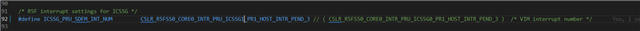

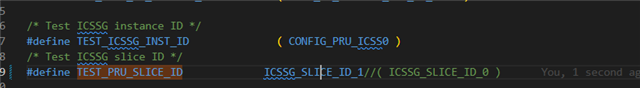

/* Test ICSSG instance ID */ #define TEST_ICSSG_INST_ID ( CONFIG_PRU_ICSS0 ) /* Test ICSSG slice ID */ #define TEST_ICSSG_SLICE_ID ( ICSSG_SLICE_ID_1 ) /* Test PRU core instance IDs */ #define TEST_PRU_INST_ID ( PRUICSS_PRU1 ) #define TEST_RTU_INST_ID ( PRUICSS_RTU_PRU1 ) /* R5F interrupt settings for ICSSG */ #define ICSSG_PRU_SDDF_INT_NUM ( CSLR_R5FSS0_CORE0_INTR_PRU_ICSSG1_PR1_HOST_INTR_PEND_3 ) /* VIM interrupt number */ #define ICSSG_RTU_SDDF_INT_NUM ( CSLR_R5FSS0_CORE0_INTR_PRU_ICSSG1_PR1_HOST_INTR_PEND_4 ) /* VIM interrupt number */ #define ICSSG_TX_PRU_SDDF_INT_NUM ( CSLR_R5FSS0_CORE0_INTR_PRU_ICSSG1_PR1_HOST_INTR_PEND_5 ) /* VIM interrupt number */

IEP 时钟更改为200MHz

/* Test Sdfm parameters */

SdfmPrms gTestSdfmPrms = {

200000000, /*Value of IEP clock*/

20000000, /*Value of SD clock (It should be exact equal to sd clock value)*/

0, /*enable double update*/

10, /*first sample trigger time*/

0, /*second sample trigger time*/

APP_EPWM_OUTPUT_FREQ, /*PWM output frequency*/

{{3500, 1000}, /*threshold parameters(High, low )*/

{3500, 1000},

{3500, 1000}},

{{0,0}, /*clock sourse & clock inversion for all channels*/

{0,0},

{0,0}},

15, /*Over current osr: The effect count is OSR + 1*/

64, /*Normal current osr */

0, /*comparator enable*/

(uint32_t)&gSddfChSamps /*Output samples base address*/

};

在函数 init_sddf 中、 CSL_PRU_ICSSG0_PR1_CFG_SLV_BASE 更改为 CSL_PRU_ICSSG1_PR1_CFG_SLV_BASE

/* Configure g_mux_en to PRUICSS_G_MUX_EN in ICSSG_SA_MX_REG Register. */

HW_WR_REG32((CSL_PRU_ICSSG1_PR1_CFG_SLV_BASE+0x40), PRUICSS_G_MUX_EN);

其余与 PWM 相关的更改。 可以正常进入 PWM 中断 App_epwmIntrISR、PWM 输出保持50%。

谢谢!

建宇