主题中讨论的其他器件:SysConfig、

工具与软件:

嗨、团队:

您能否就我的客户提出的以下问题提供反馈?

1. 我们想问您关于时钟的问题。

LFCLK 和 ULPCLK 之间有何区别? 我想告诉我如何正确使用它。

此外、何时使用"MFCLK"? 请告诉我如何将其与"MCLK"配合使用。

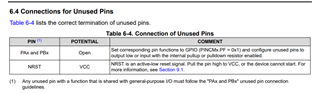

2. 我们想问您几个有关处理未使用的引脚的问题。

①如下面的"注释"列中所述、它们是否必须为所有未使用的引脚将输出和输入分配给 GPIO? 或者是否可以简单地不在 SysConfig 中分配引脚?

②使用内部上拉/下拉时、此电阻器的阻值是多少?

③在配置用户程序之前、了解内部上拉和下拉均已禁用(即 IO 引脚为 Hi-Z)是否正确?

④In 日本版的硬件开发指南,它写在下表的"注意"部分,你可以参考连接指南的未使用引脚的"PAx",但他们找不到它。

他们可以从哪里查看?

提前感谢您。

此致、

Kenley