https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1094892/tlv320aic3254-clock-ratio

部件号:TLV320AIC3254大家好,

客户使用TLV320AIC3254。 此DSP被设置为从属设备,其数字I2S数据和时钟来自另一个IC。 DSP的比特时钟与帧同步比为80fs。 帧时钟是标准48kHz,但这意味着主时钟以3.84MHz运行。 (实际上,他们看到~4MHz。)

这对他们来说很奇怪。 它们通常采用二倍功耗比,在这种情况下,通常使用64fs。 比特时钟将是3.072MHz,这是熟悉和舒适的,而不是4MHz左右。

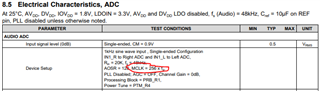

数据表中唯一相关的内容是规格表中全部显示MCLK = 256fs,如下所示:

虽然设计可行,但具有这样的时钟比率是相当罕见的。 您能告诉我们为什么要这样做吗? 此DSP是否有任何特殊之处,使80fs成为必需或有益的? 即使有,64fs仍能正常工作吗?

谢谢!

康妮