请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TLV320AIC3120 - 在我们的定制项目中、我们将编解码器(TLV320AIC3120IRHBT)连接到声码器(AMBE-4020全双工 BGA)。在 I2S 中将数字音频数据发送到声码器。

- I2S 接口的计算值为 wrt to 声码器:

- I2S 将在 DSP 主控模式下运行

- I2S 接口允许 AMBE-4020 接收和发送8kHz 语音数据(请参阅 AMBE-4020全双工 BGA 的2.11)、即 WS/FS/LRCLK/WCLK = 8kHz

- 字长= 16

- 通道数= 2

- SCLK/BCLK = WCLK x 字长 x 通道数= 8kHz x 16 x 2 = 256kHz

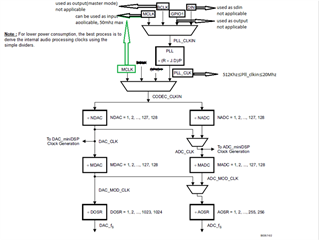

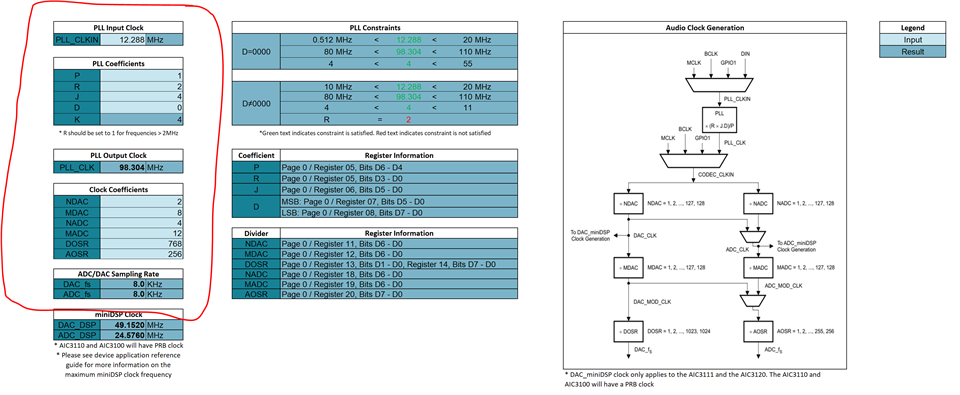

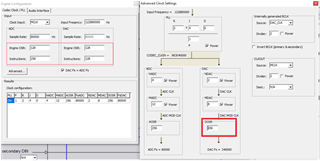

- ADC 的编解码器时钟计算:

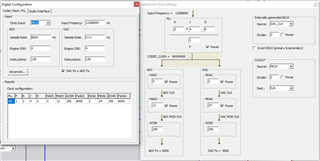

按照第7.3.10.8节第1步中提到的步骤和第7.3.13节中提到的时钟计算进行操作。 插入的图像供参考

- 目标 ADC 采样频率(ADC_FS)= 8kHz、由上文所述的2.b 得出。

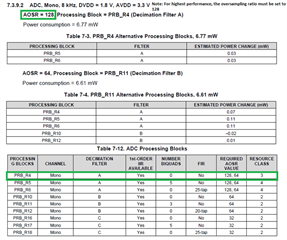

- 抽取滤波器= A

- AOSR = 128、

通过引用第7.3.9.2节选择 b、c 值

- 因此、ADC_FS x AOSR = 8kHz x 128 = 1024kHz = ADC_MOD_CLK。 因此,假设2800Khz≤AOSR*ADC_FS≤6200Khz (在第3.10.8节中),但这种情况不能满足,如何解决这个问题?

- mAdc 的值应该被选择、这样它满足条件 mAdc*(AOSR/32)>=RC。 因此选择的 mAdc = 1。 mAdc 的计算是否正确? 由于在文件中说它可以在1到128的范围内、因此没有提供有关这方面的进一步信息。

- 因此、如果选择的 mAdc 正确、则 ADC_CLK = ADC_MOD_CLK x mAdc = 1024kHz x 1 = 1024 kHz。 请建议 ADC_CLK 的频率及其范围在什么基础上取决于?

- 为获得 CODE_CLK、应选择多少 NADC 的值(CODE_CLK = NADC x ADC_CLK)。 请建议 CODE_CLK 的频率和范围在什么基础上取决于?

- 此外、如果在内部 PLL 输入被用作 CODEC _CLK 并且提供了 MCLK 作为 PLL 的输入、请建议 PLL 和 MCLK 的频率值。