您好、专家、

我收到 了有关 PCM1862时钟暂停和错误检测的问题。

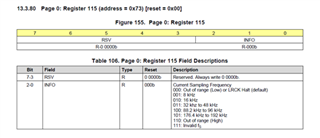

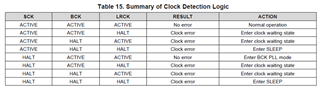

当 CLK 在没有如下 CLK 暂停的情况下发生更改时、从44.1kHz x 更改为48kHz、它是否会被视为 CLK 误差?

SCLK 22.579MHz⇒24.576MHz

BCLK 2.822MHz ⇒3.072MHz

LRCK 44.1kHz ⇒48kHz

如果是、PCM1862是否应在检测到 CLK 错误后自动重新运行、步骤如下、该步骤以9.3.9.7时钟停止和错误检测的形式编写?

1.立即使音频输出静音(无音量下降)

2.等待提供正确的时钟(称为时钟等待状态)

3.重新启动时钟检测。 PLL 和所有时钟分频器根据检测结果进行重新配置。

4.开始淡入

此致、

小岛