您好!

在定制电路板上配置 DAC3100后、我遇到了 I2C 通信问题、它定期读取和写入 NAK、从不恢复。 我直接从以前的定制板硬件版本移植了我的驱动程序、该版本已经使用多年。 我很难理解为什么驱动程序在新硬件上显示 I2C 通信错误。

/* an array of address/value pairs */

static const uint8_t aInitRegs[] = {

0x00, 0x00, // select page 0

0x01, 0x01, // software reset

0xFE, 1, // delay 1 ms (Parser implements via vTaskDelay())

0x00, 3, // page 3

0x10, 0x01, // use internal osc for delay timers

0x00, 0x00, // select page 0

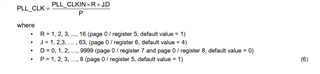

0x04, 0x03, // PLL_CLKIN=MCLK, CODEC_CLKIN=PLL_CLK

0x05, 0x11,

0x06, 40, // set PLL for DAC_FS=8KHz: J=40, R=1, D=0, P=1

0x05, 0x91,

0xFE, 10, // delay 10 ms (Parser implements via vTaskDelay())

0x0B, 0x81, // NDAC=1

0x0C, 0x90, // MDAC=16

0x0D, 0x02, // DOSR=640

0x0E, 0x80,

0x1B, 0x00, // mode I2S, wordlength 16, slave mode

0x3C, 4, // processing block 4

0x00, 0x08, // select page register 8

0x01, 0x04, // turn on adaptive filtering

0x00, 0x01, // analog blocks, select page register 1

0x23, 0x40, // LDAC routed to mixer/amp, RDAC not routed anywhere

0x2A, 0x04, // unmute class-D, 6 dB gain

0x20, 0x86, // power-up class-D

0x26, 0x8C, // left analog volume routed to class-D, vol = -6 dB

0x00, 0x00, // page 0

0x3F, 0xB0, // LDAC on, RDAC off, LDAC=(L+R)/2

0x41, 0x30, // LDAC gain 24 dB

0x42, 0x81, // RDAC gain -63 dB

0x40, 0x00, // unmute L,R channels

};i2c=1,2,30,00,00 Test I2C write I2C write - Slave Addr: 0x30, Register: 0x00, Payload: 0x00 > i2c=0,2,30,04,1 Test I2C read I2C read - Slave Addr: 0x30, Register: 0x04, Number of bytes: 1 Received: 0x03 > i2c=0,2,30,05,1 Test I2C read I2C read - Slave Addr: 0x30, Register: 0x05, Number of bytes: 1 Received: 0x91 > i2c=0,2,30,06,1 Test I2C read I2C read - Slave Addr: 0x30, Register: 0x06, Number of bytes: 1 Received: 0x28 > > i2c=0,2,30,FE,1 Test I2C read I2C read - Slave Addr: 0x30, Register: 0xFE, Number of bytes: 1 I2C read failed > i2c=0,2,30,0B,1 Test I2C read I2C read - Slave Addr: 0x30, Register: 0x0B, Number of bytes: 1 I2C write failed I2C read failed

> > > i2c=1,2,30,00,00 Test I2C write I2C write - Slave Addr: 0x30, Register: 0x00, Payload: 0x00 > > > i2c=0,2,30,04,1 Test I2C read I2C read - Slave Addr: 0x30, Register: 0x04, Number of bytes: 1 Received: 0x00 > i2c=0,2,30,05,1 Test I2C read I2C read - Slave Addr: 0x30, Register: 0x05, Number of bytes: 1 Received: 0x11 > > i2c=0,2,30,06,1 Test I2C read I2C read - Slave Addr: 0x30, Register: 0x06, Number of bytes: 1 Received: 0x04 > > i2c=0,2,30,FE,1 Test I2C read I2C read - Slave Addr: 0x30, Register: 0xFE, Number of bytes: 1 Received: 0x00 > > i2c=0,2,30,0B,1 Test I2C read I2C read - Slave Addr: 0x30, Register: 0x0B, Number of bytes: 1 Received: 0x01 > > i2c=0,2,30,0C,1 Test I2C read I2C read - Slave Addr: 0x30, Register: 0x0C, Number of bytes: 1 Received: 0x01 > > i2c=0,2,30,0D,1 Test I2C read I2C read - Slave Addr: 0x30, Register: 0x0D, Number of bytes: 1 Received: 0x00 > > i2c=0,2,30,0E,1 Test I2C read I2C read - Slave Addr: 0x30, Register: 0x0E, Number of bytes: 1 Received: 0x80 > > i2c=0,2,30,1B,1 Test I2C read I2C read - Slave Addr: 0x30, Register: 0x1B, Number of bytes: 1 Received: 0x00 > > i2c=0,2,30,3C,1 Test I2C read I2C read - Slave Addr: 0x30, Register: 0x3C, Number of bytes: 1 Received: 0x01 > > i2c=1,2,30,00,08 Test I2C write I2C write - Slave Addr: 0x30, Register: 0x00, Payload: 0x08 > > i2c=0,2,30,01,1 Test I2C read I2C read - Slave Addr: 0x30, Register: 0x01, Number of bytes: 1 Received: 0x00 > > i2c=1,2,30,00,01 Test I2C write I2C write - Slave Addr: 0x30, Register: 0x00, Payload: 0x01 > > i2c=0,2,30,23,1 Test I2C read I2C read - Slave Addr: 0x30, Register: 0x23, Number of bytes: 1 Received: 0x00 > > i2c=0,2,30,2A,1 Test I2C read I2C read - Slave Addr: 0x30, Register: 0x2A, Number of bytes: 1 Received: 0x00 > > i2c=0,2,30,20,1 Test I2C read I2C read - Slave Addr: 0x30, Register: 0x20, Number of bytes: 1 Received: 0x06 > > i2c=0,2,30,26,1 Test I2C read I2C read - Slave Addr: 0x30, Register: 0x26, Number of bytes: 1 Received: 0x7F > > i2c=1,2,30,00,00 Test I2C write I2C write - Slave Addr: 0x30, Register: 0x00, Payload: 0x00 > > i2c=0,2,30,3F,1 Test I2C read I2C read - Slave Addr: 0x30, Register: 0x3F, Number of bytes: 1 Received: 0x14 > > i2c=0,2,30,41,1 Test I2C read I2C read - Slave Addr: 0x30, Register: 0x41, Number of bytes: 1 Received: 0x00 > > i2c=0,2,30,42,1 Test I2C read I2C read - Slave Addr: 0x30, Register: 0x42, Number of bytes: 1 Received: 0x00 > > i2c=0,2,30,40,1 Test I2C read I2C read - Slave Addr: 0x30, Register: 0x40, Number of bytes: 1 Received: 0x0C >