你好

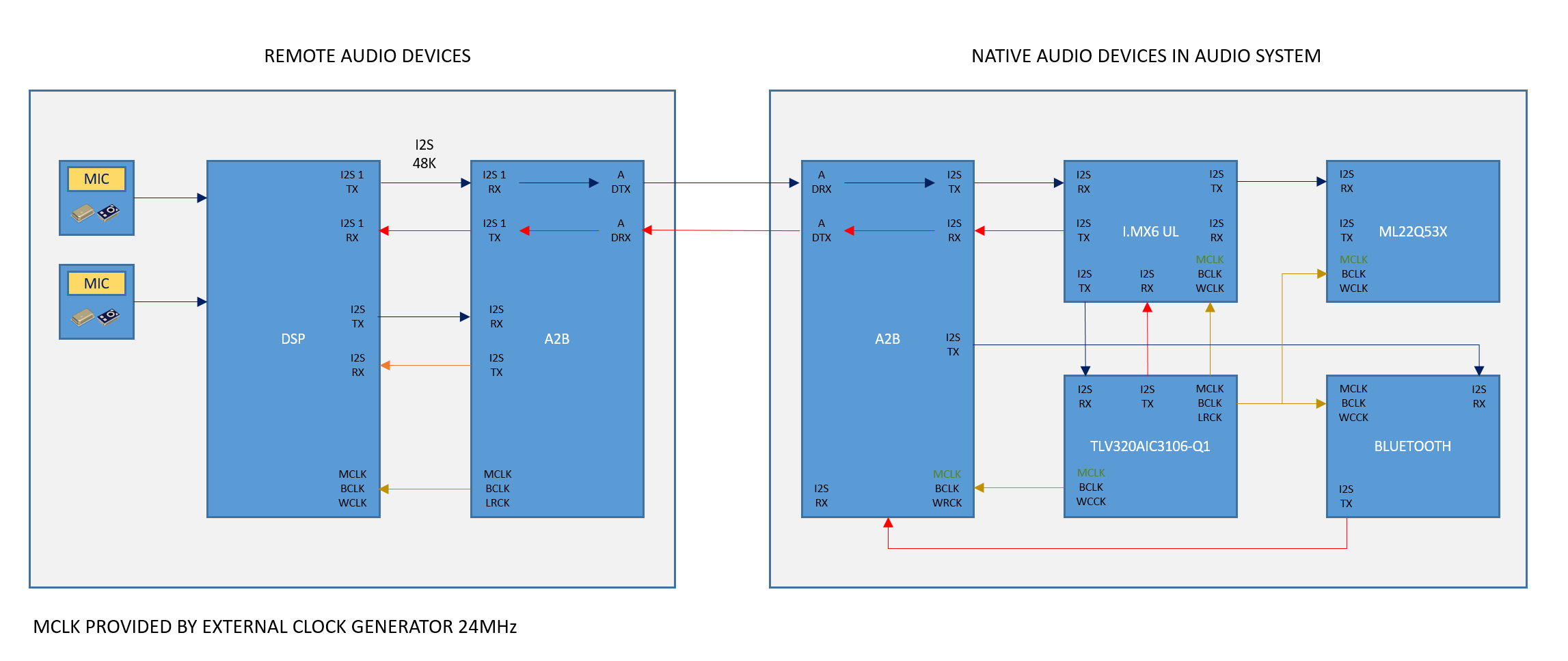

我们在此设计 TLV320AIC3106-Q1。 在我们的系统中、这里有如下所示的各种音频器件、 我们希望所有器件都通过一个主器件 TLV320AIC3106-Q1提供的共享时钟设置为从器件。

1.蓝牙 I2S/Jody-W3.

蓝牙免提中使用的 I2S (PCM 格式)

2.使用 A2B 总线电源的 A2B 主收发器/AD2428W 和具有从节点的 A2B 网络

用于外部麦克风和 AECNR 模块的 I2S 主 A2B 总线

2-1. A2B 从收发器/AD2428W

与 ZL38080 DSP 连接的 I2S 从收发器

2-2. 用于 麦克风输入的 ZL38080 A DSP (远程 SLACE)

用于 AEC-NR 的 I2S 从远程 DSP

3.语音 IC/ Lapis ML22530

4.应用处理器 I.MX6 UL

这里有3个 I2S (SAI)接口、它们设置为从(由于 NXP 应用处理器 I.MX6 UL AUDMUX IP 问题)。 一个用于编解码器/另一个用于 AD2428W A2B 主设备/另一个用于 ML22530

根据所选编解码器的数据表、当我们将编解码器搜索为 I2S 主模式参数时、此处没有关于此用例的更多信息。 在输出设计案例中、TLV320AIC3106-Q1是列出的音频器件唯一一个通用主器件。 我们必须知道编解码器中 BCLK/MCLK/WCLCK (通常为外部参考24MHz)的扇出/驱动能力。 总之、我们想知道、编解码器是否可以为所有 I2S 从器件提供 BCLK/MCLK?