您好、支持团队

目前、在 PR 事件期间、产生了48个单元、但两个单元具有不同的音频级别测量。

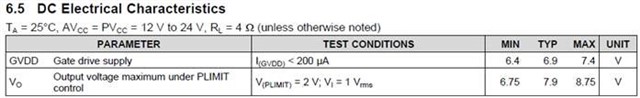

电路条件:P 限制最大值、36dB 增益

工作条件:1kHz 正弦波播放、AMP 输入电平(RMS:42mV)

- 46个单元:1.5V 输出

2个单元:1.9V 输出

出于上述原因、GVDD、增益和 P 限值的测量方法如下。

|

PR일반품 μ A |

PR이상품 μ A |

|

|

GVDD |

6.94V |

6.75伏 |

|

P_LIMIT |

6.94V |

6.75伏 |

|

增益 |

2.65伏 |

2.59伏 |

如上所述、我们正在研究某些产品具有低 GVDD 输出的原因。

目前、GVDD 仅用于增益和 P 限制设置。

此外、电阻值根据 TI 指南进行设置、但某些产品的 GVDD 电压较低。

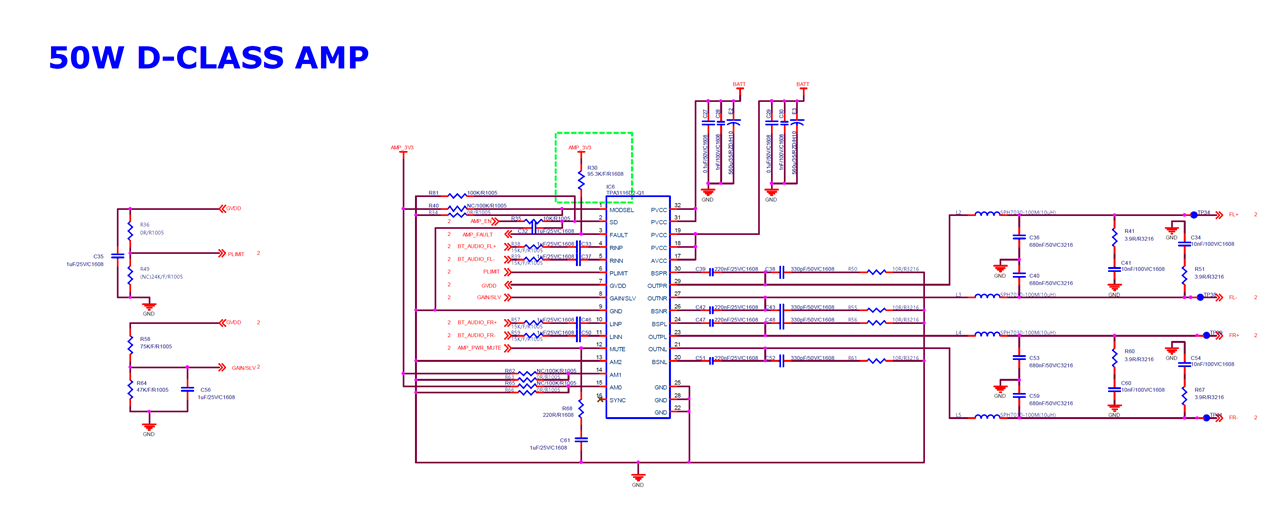

请发送下面的电路图、查看电路配置和容量值。

谢谢。

此致、

mj