https://e2e.ti.com/support/audio-group/audio/f/audio-forum/982843/adc5140evm-pdk

器件型号:ADC5140EVM-PDK你(们)好,先生

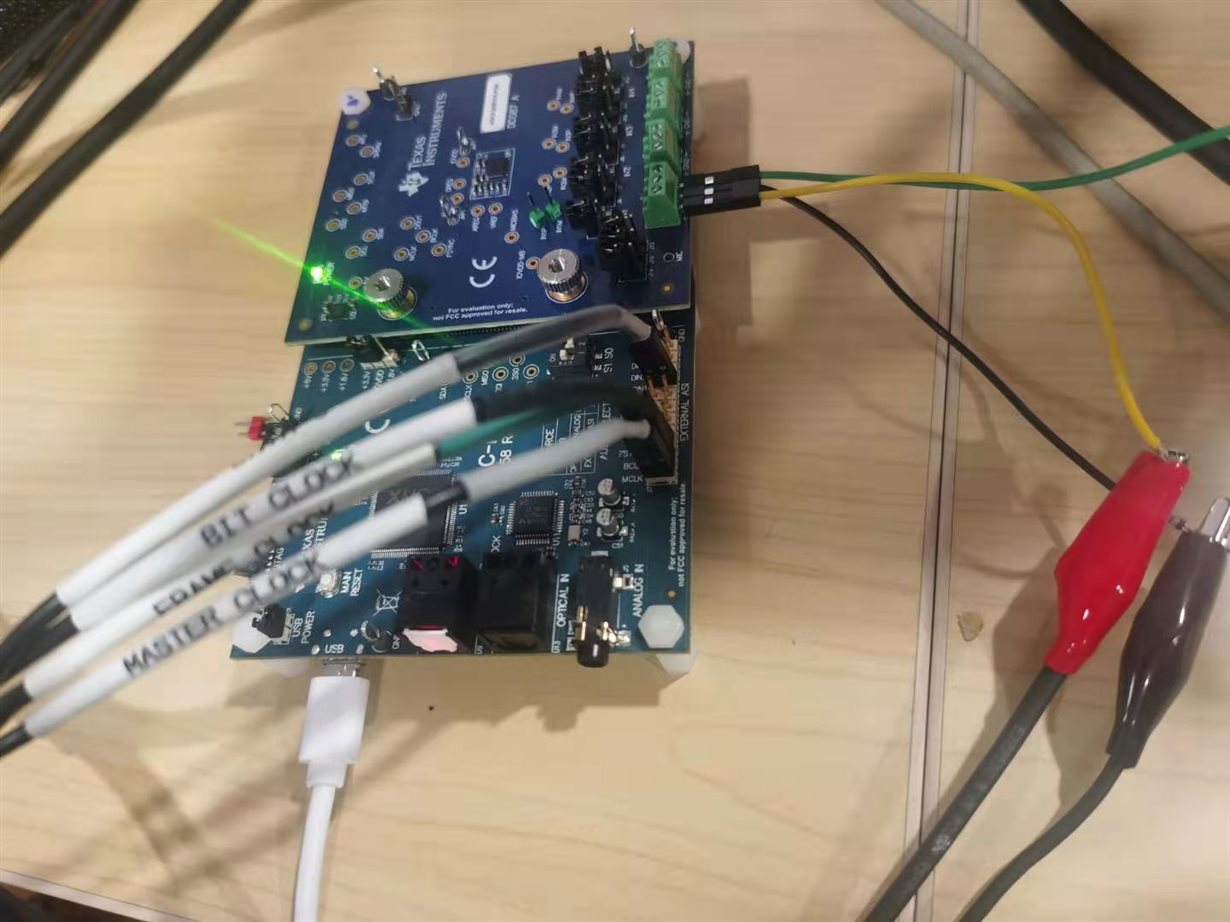

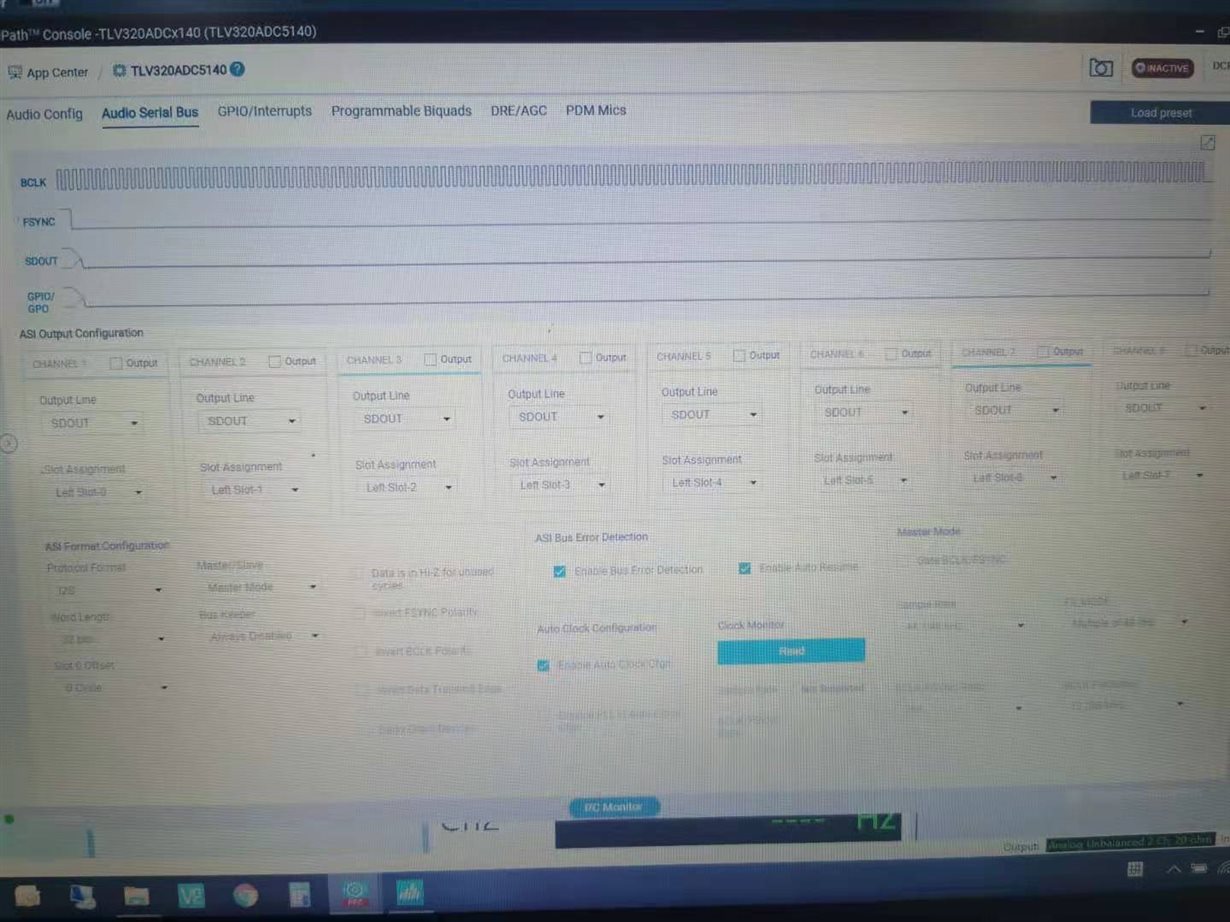

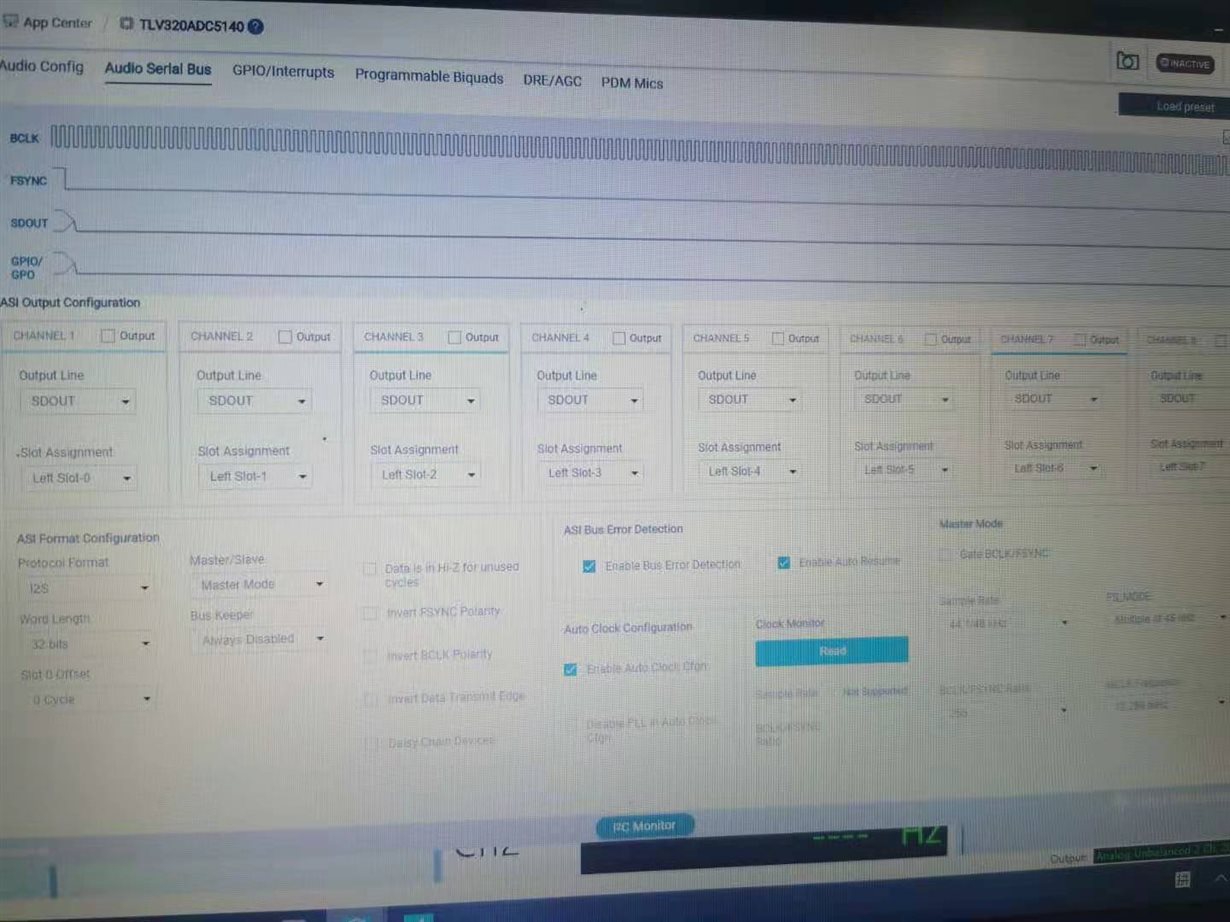

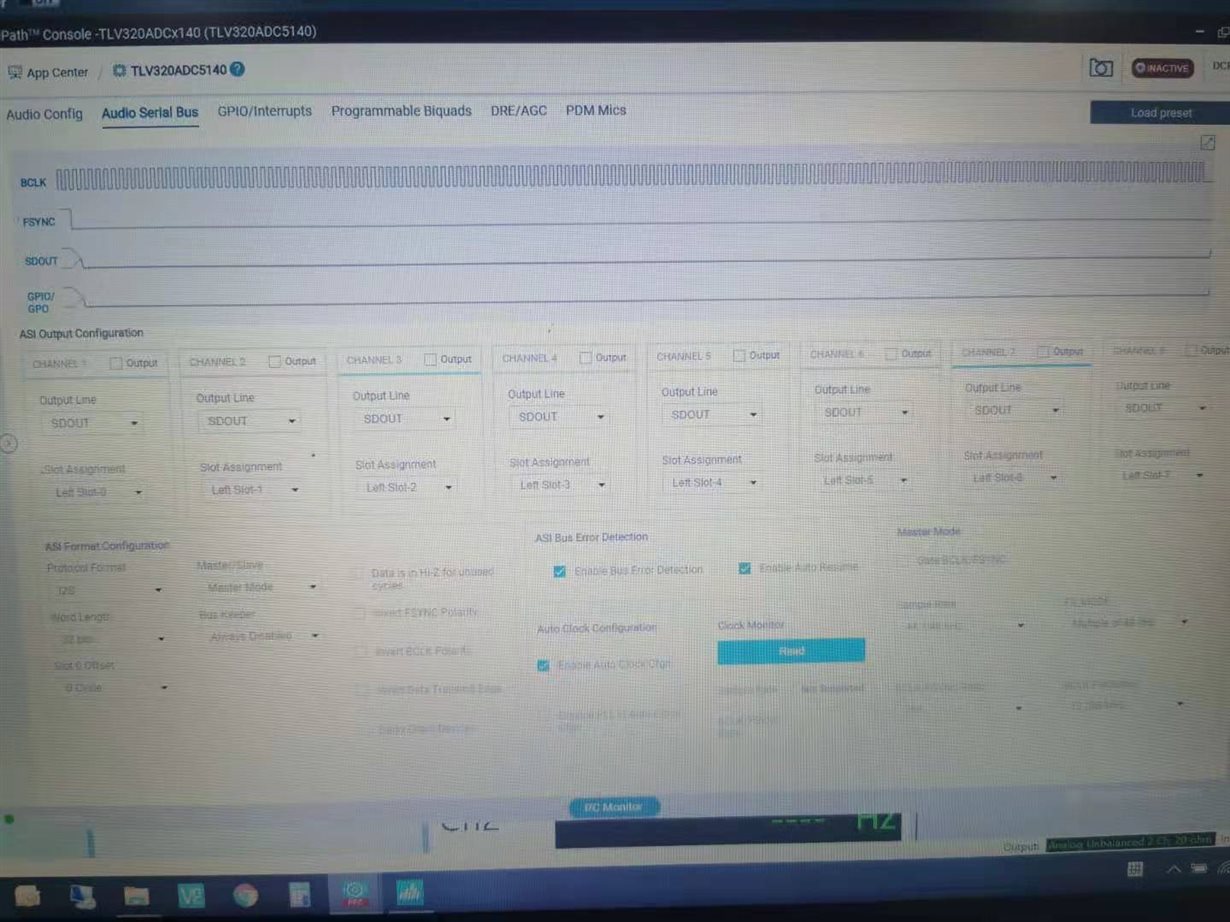

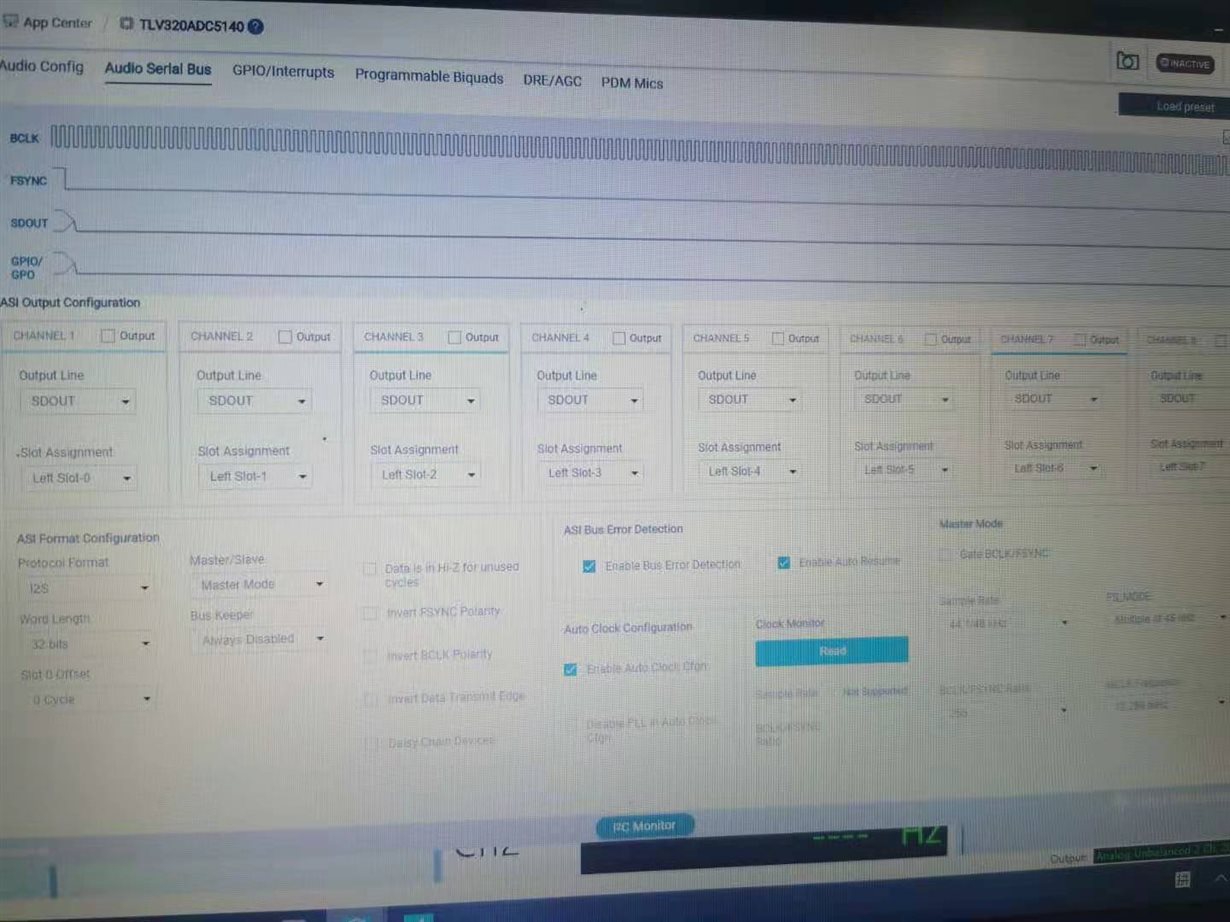

对于上述测试路径、ADC5140的 IIS 输出是主器件、同步时钟数据被发送到 AP。

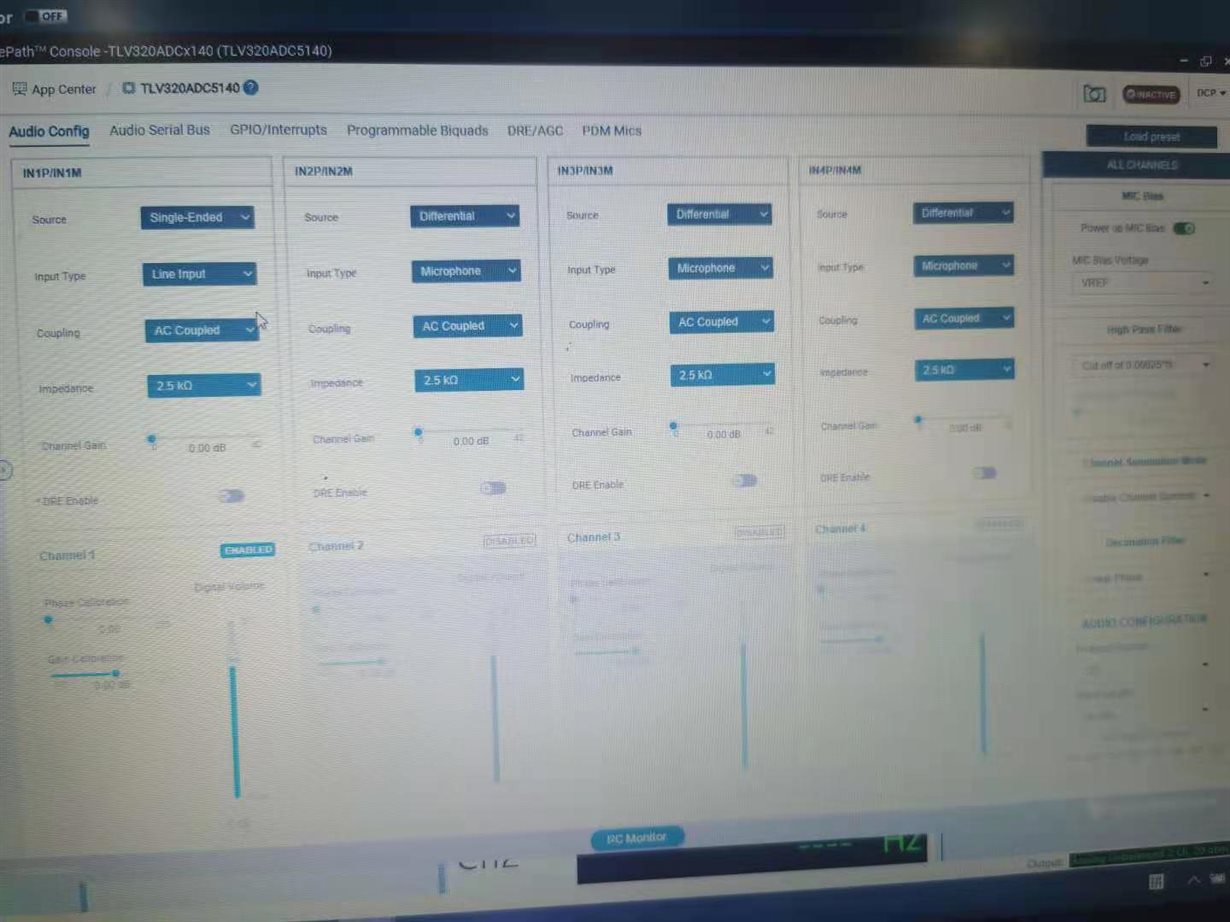

但是 找到了板 IIS 引脚,没有波形,我想,ADC5140配置错误吗?

请帮助我检查???

不支持时钟监控帧时钟、

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

https://e2e.ti.com/support/audio-group/audio/f/audio-forum/982843/adc5140evm-pdk

器件型号:ADC5140EVM-PDK你(们)好,先生

对于上述测试路径、ADC5140的 IIS 输出是主器件、同步时钟数据被发送到 AP。

但是 找到了板 IIS 引脚,没有波形,我想,ADC5140配置错误吗?

请帮助我检查???

不支持时钟监控帧时钟、

让我总结一下:

有两 个测试场景:

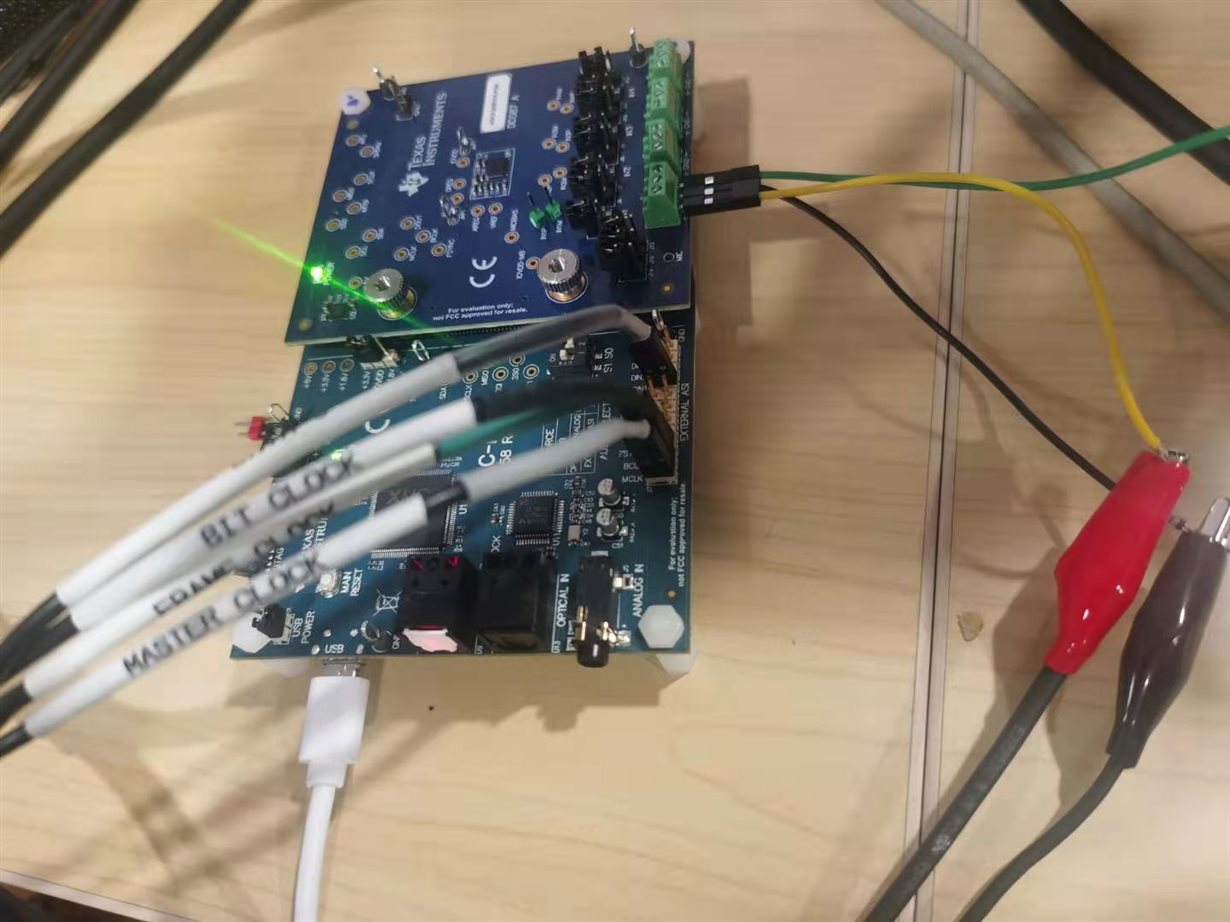

1.带有主设备的 AP、带有从设备的 adc5140 ASI、那么硬件接线 GND 在电路板内部吗?

2.ap with slave、adc5140 ASI with master、so the hardware wiring GND is outside the board?(与从属设备相映射、adc5140 ASI 与主设备相映射、那么硬件接

3.在这两种情况下,S0开关都被拨至“关闭”?

4、我们用编解码器 MCLK、FRAMECLK 测试板测试引脚... wav 错误、信号质量差

在下一个主题中:

1) 打开时开关 S0

S0应仍处于"关闭"位置、以便将 AP 与 EVM 配合使用。

2.ap 与从器件、ADC5140 ASI 与主器件、我是否 将硬件接线 GND 置于电路板外部、

良好、GND 在电路板外部。 您仍需要确保 AP 输出 BCLK 信号、以便 ADCx140可以使用它来生成 FSYNC 和 DOUT 输出。

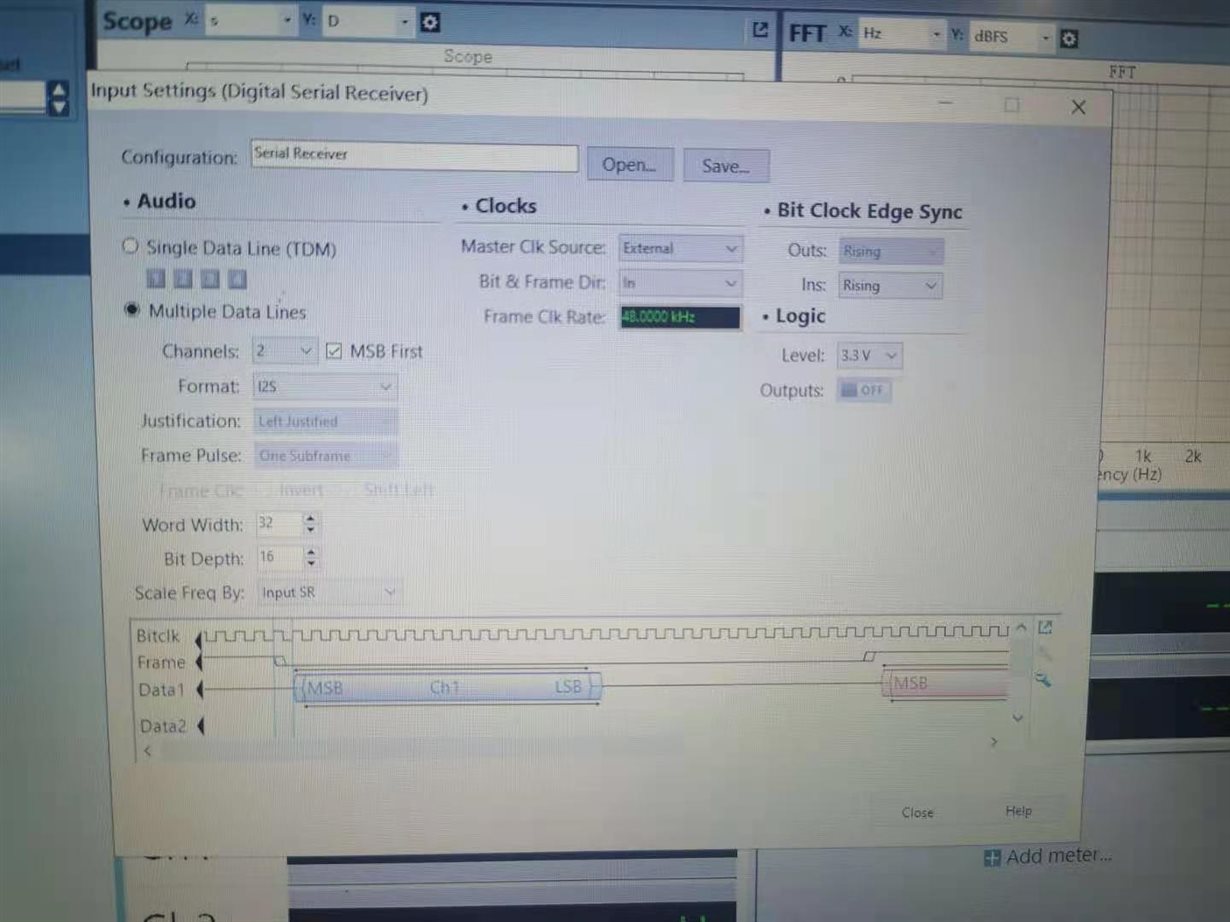

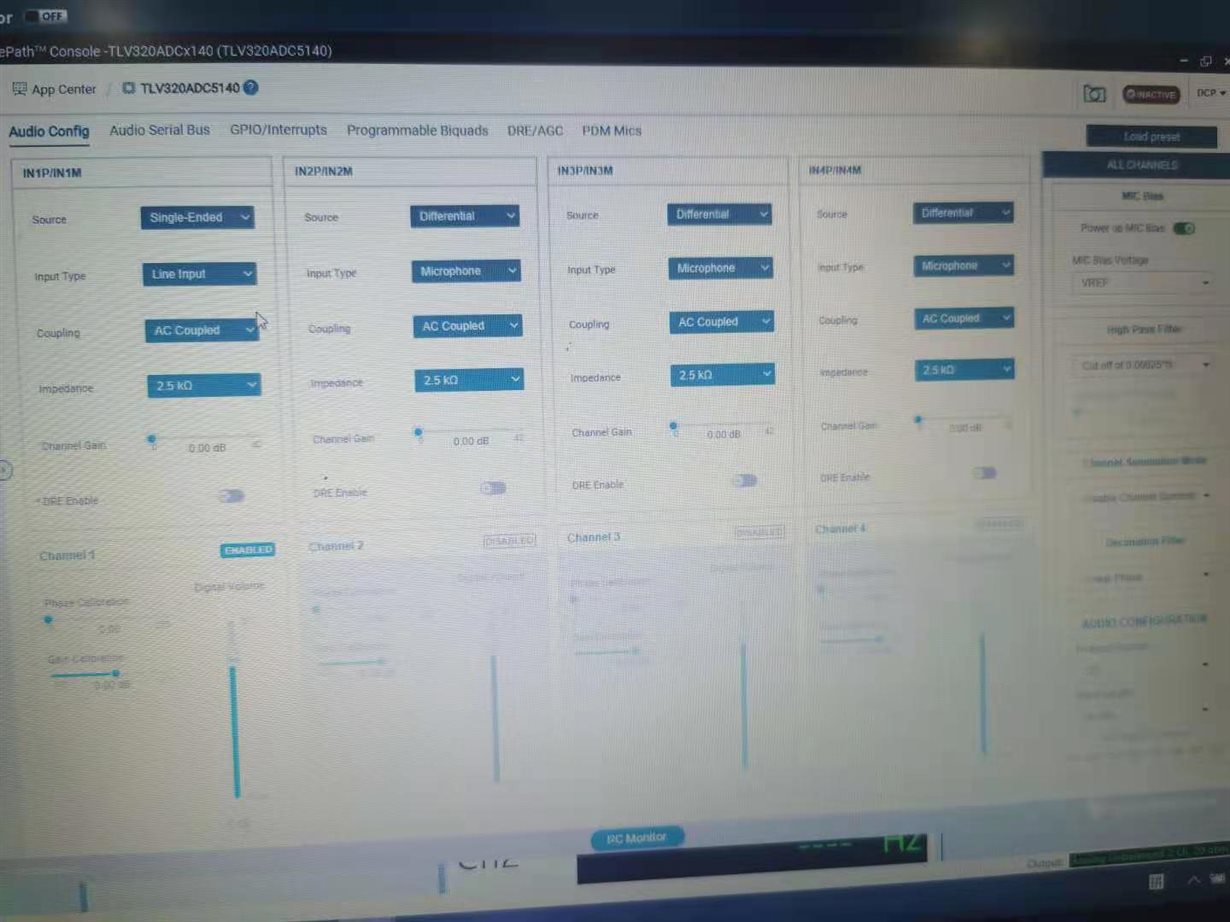

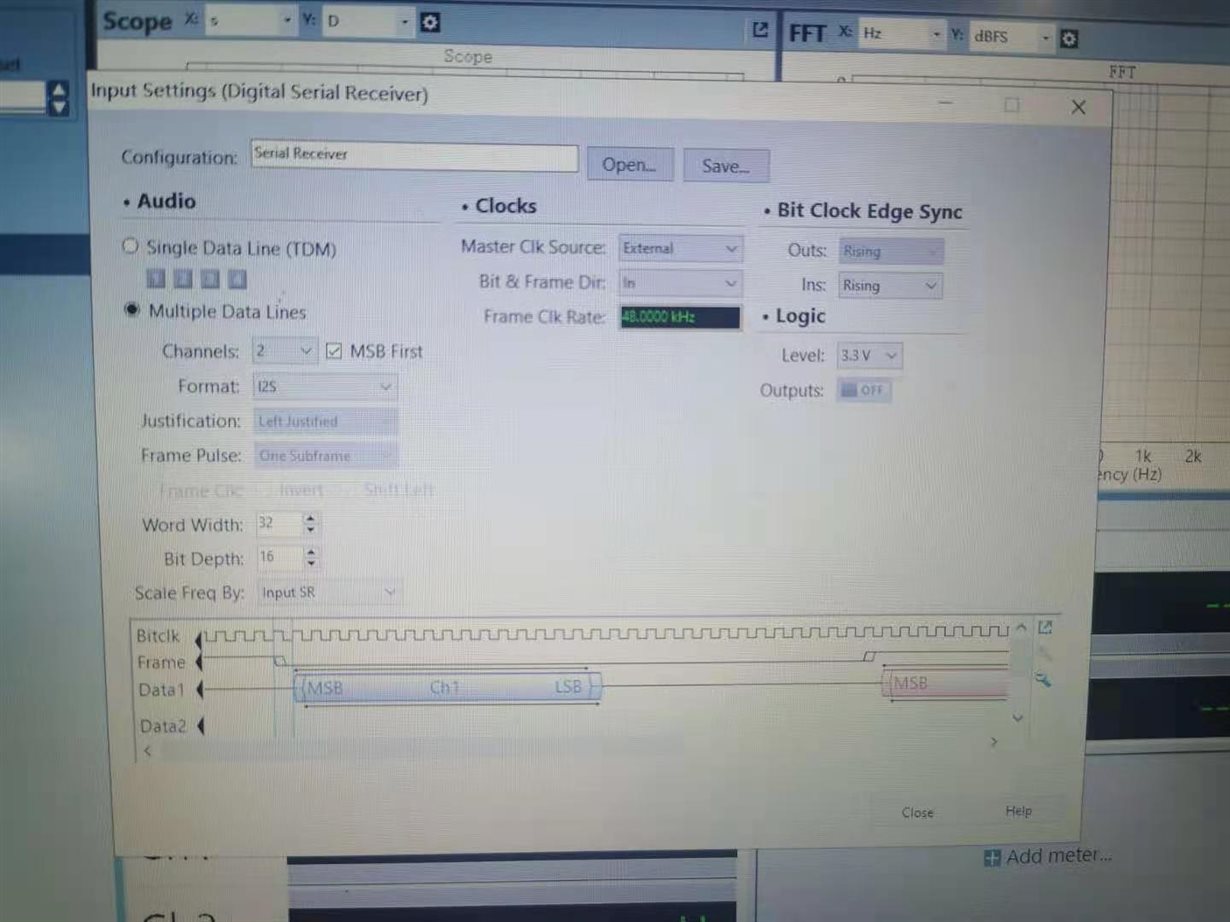

3、ap digtal serial with TDM mode、with word len 32位、I config one ended single channel、so ap with 2 channel num。

这些设置看起来是正确的、但 CH2未在主模拟页面上启用、即使它已与插槽1对插槽。

您好、先生、

在下一个主题中:

1) 打开时开关 S0

S0应仍处于"关闭"位置、以便将 AP 与 EVM 配合使用。

2.ap 与从器件、ADC5140 ASI 与主器件、我是否 将硬件接线 GND 置于电路板外部、

良好、GND 在电路板外部。 您仍需要确保 AP 输出 BCLK 信号、以便 ADCx140可以使用它来生成 FSYNC 和 DOUT 输出。

3、ap digtal serial with TDM mode、with word len 32位、I config one ended single channel、so ap with 2 channel num。

这些设置看起来是正确的、但 CH2未在主模拟页面上启用、即使它已与插槽1对插槽。

我与您一起测试建议您检查我的随员