主题中讨论的其他器件: PCM1794、 PCM1794A

您好!

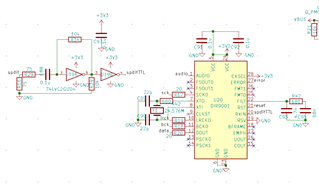

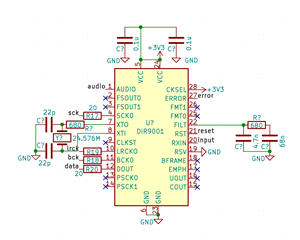

首先、我对有关晶振或 PPL 选择的文档有点困惑。 网络上的一个图使用了一个晶体、CLKSEL 引脚悬空(因此通过下拉接地)、但我认为它应该保持高电平、并且 FMT0/1可以保持原样、因为它们不会产生任何影响。 是这样吗?

第二个问题、我从计算机主板获取 SPDIF。 计算机和 dir9001+pcm1794+运算放大器将共享相同的接地。 虽然通常使用隔离变压器、但除了尖峰保护之外、我看不到它的需求、我想知道它是否像直接连接 RXIN 引脚那样简单。 但是、我尚未测量到 SPDIF 电压过高、但很快就会测量到。

第三个问题、是否所有使用加重的44KHz 样本或是否有自动检测的方法? 我想知道 emphh 引脚是否会提供此检测、以及是否可以使用它来自动设置 PCM1794上的去加重引脚。 在大多数情况下、它看起来像是一段很长的时间没有使用过预加重、我可能会忽略它、但值得检查。