主题中讨论的其他器件:TAS5414

我在尊敬的 TI 工程师 Greg Scott 的支持下、开始了 TAS5414/5424设计。 出色的 TI 技术支持! 格雷格正在比赛中。

客户的高层管理人员将此项目提交到我的议程中、但最近我非常紧迫地将其重新列入议程。

如果我将运算放大器放置在 TAS5414输入之前、此设计将非常有效。 这是一个非音频、直流耦合应用、在 TAS54xx 的输入端没有数据表中建议的耦合电容器。

要成功实现这一目标、我需要知道 TAS54xx 的共模电压范围。 该部件的最高增益为40 (->32dB)、因此驱动轨到轨输出需要大约600mV p-p 的差分输入电压。

数据表表示内部直流偏置点为~3.3VDC、共模范围为1800mV 峰间值、以3.3VDC 为中心。 我的理解是、对于零差分输入电压、共模范围为2.4-4.2VDC。

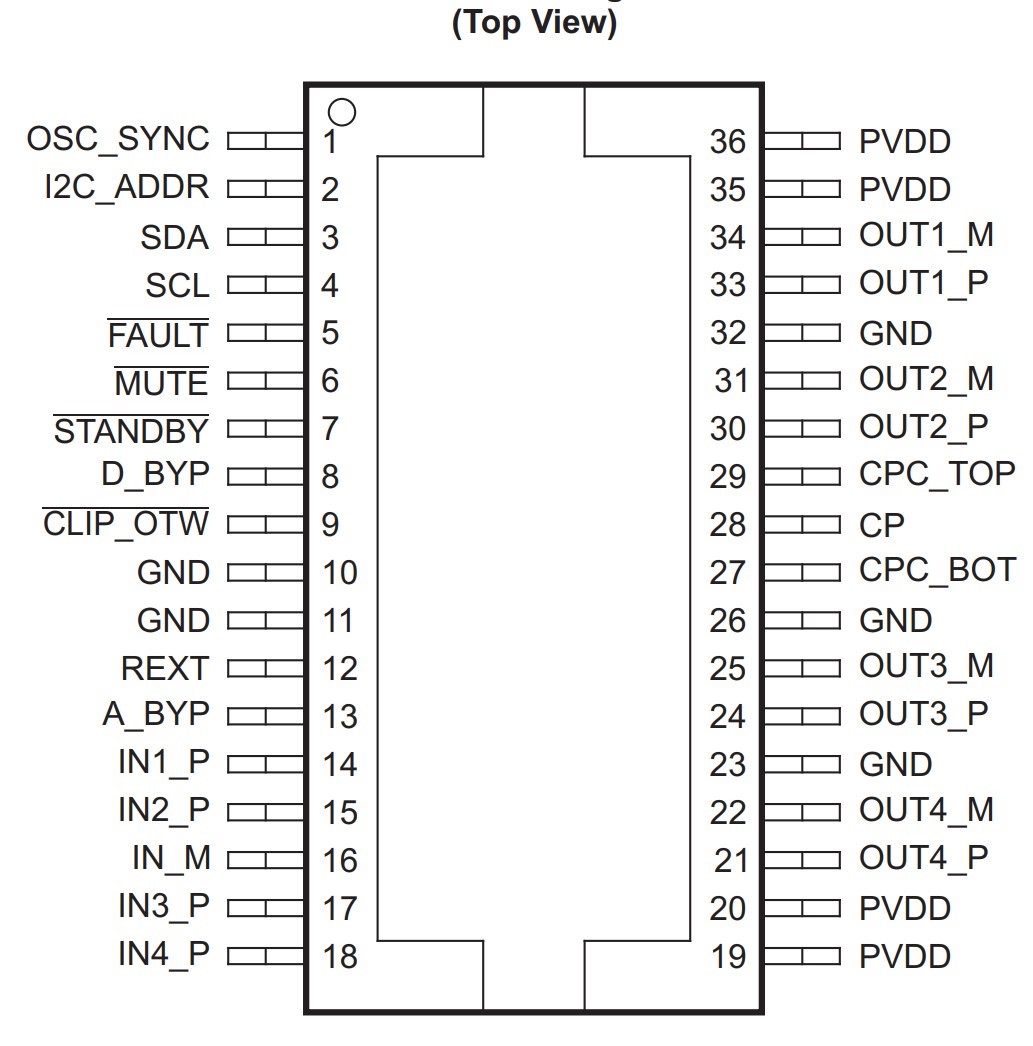

这是否意味着我可以在 IN_M 公共偏置引脚上施加4.0VDC 等电压、并且仍然能够在不失真的情况下驱动 D 类轨到轨输出? 我可以将 IN-M 引脚偏置为高于4V 吗?

假设我保持在器件的共模范围内、将4V 强制施加到 IN_M 引脚上是否存在任何问题?

或者、如果我能够熟练地让器件在3.3VDC 下自偏置其输入、我能否使用运算放大器对该内部偏置电压进行"采样"并使用该电压对我的外部运算放大器进行偏置?

数据表提示使用85k 电阻器建立内部偏置点。 大声地思考、这意味着使用具有1nA 偏置电流的运算放大器对偏置电压进行采样将"将"TAS54xx 的偏置点"拉至85微伏、对吧?

提前感谢您对此主题的反馈。

Jim Olson

美国印第安纳波利斯