Other Parts Discussed in Thread: PCM3168A

您好!

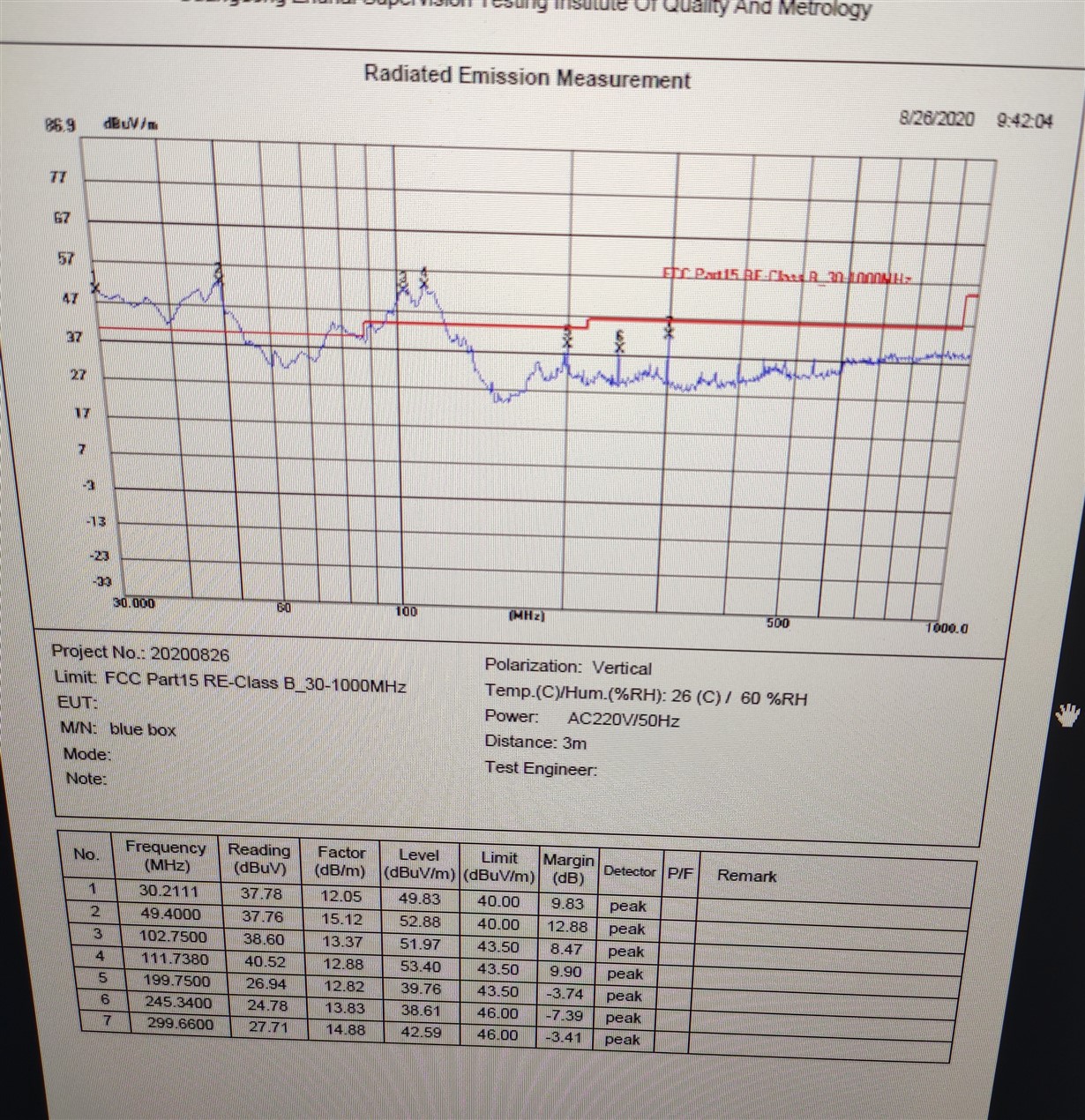

我们正在使用两个 PCM3168A 器件构建消费类产品、并且无法通过 FCC 测试。

我们的设计采用小型金属外壳、并使用两个 PCM3168A。 我们已经隔离了噪声、并相信它来自音频部分、包括编解码器。 竞争对手器件的先前设计通过了 FCC。 因此、我们认为 PCM3168A 周围的电路是问题所在。 它位于下方。

根据工厂的建议、我们在第二次通过时添加了 L16。 它似乎没有产生太大的影响。 在另一张靠近 MCU 的图纸中、MCLK、SCLK、FCLK 和 MOSI 具有100欧姆的串联电阻器。

我们在从模式、单速率时钟以及12.288MHz 的 MCLK 中使用这两种编解码器。

您对如何降低噪声有什么建议吗? 我们是否遗漏了任何东西?

非常感谢。

Aaron Higgins