大家好、

这是以下链接的最后一个问题。 请提供一些调试方向。

https://e2e.ti.com/support/audio/f/6/p/911258/3371248#3371248

我们花了一些时间来进行测试。 我们还认为它与时钟结构有关。 请参阅下面的时钟波形。

fMCLK (R18)= 12.288MHz

fI2C_clk (R19)=3.053MHz

fI2C_ws (R21)=48kHz

2寄存器设置差异

寄存器地址0x0 = 0x61

寄存器地址0x1 = 0x3

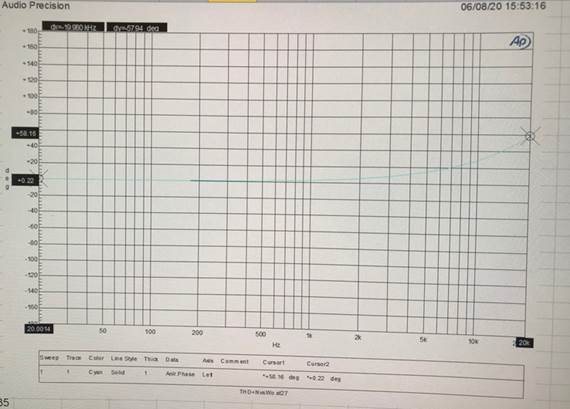

相位延迟失败:-58度

3寄存器设置差异

寄存器地址0x0 = 0x61

寄存器地址0x1 = 0x0

寄存器地址0x2 = 0x49

寄存器地址0x7 = 0x14

相位延迟通过:17.96度

THD+N 故障:-29.68 ( 规格>=60dB)

我是否可以知道是否有设置可以同时通过相位延迟和 THD+n? 请告诉我您的建议设置和调试流程。

我们希望提高调试流程的效率。 谢谢。