您好!

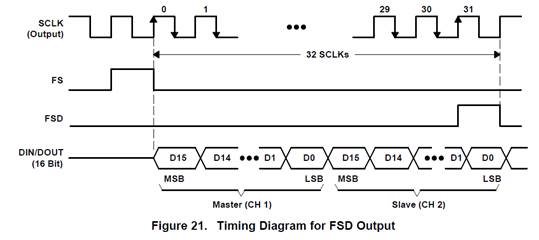

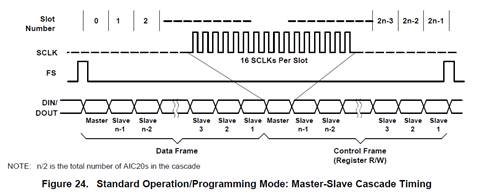

我们将在主从配置中的级联模式下使用三个 TLV320AIC24KIPFBG4以及一个 FPGA。

FPGA 配置全部三个编解码器、链中的第一个编解码器是主编解码器。

以下是编解码器配置的要求、

MCLK = 4.096MHz

Fs = 8kHz

M = 4

N = 1

P = 8

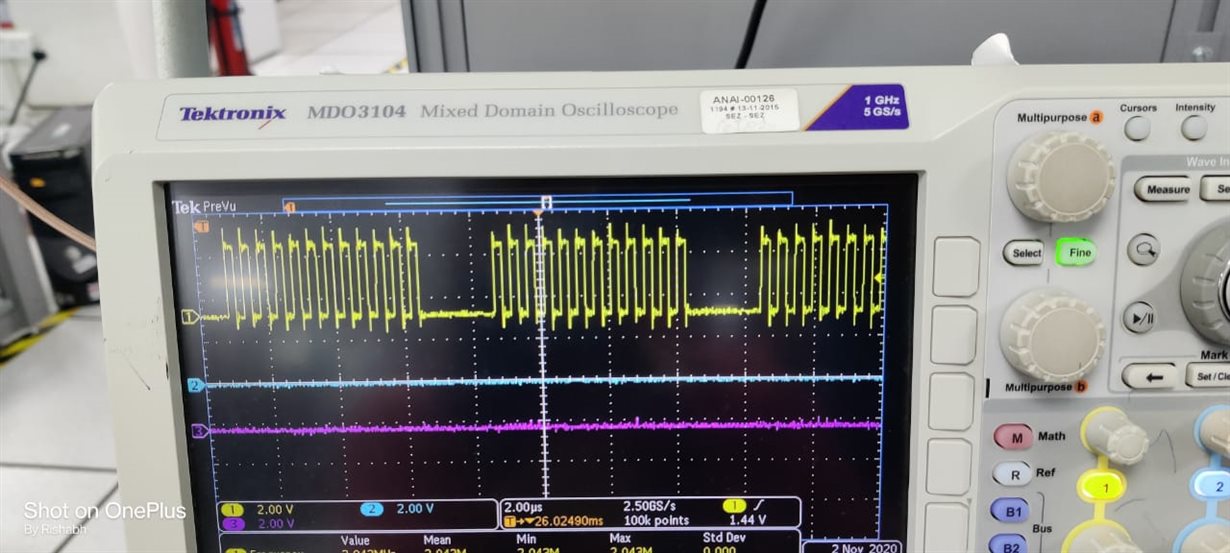

根据三种编解码器配置、我们预计 SCLK 为1.536MHz。

加电后,ACD 将正确确定三个编解码器。 但是、一旦软件配置了编解码器、我们将获得2.048MHz 的 SCLK、这意味着四个级联编解码器。

请确认我们对 SCLK 频率的理解是否正确。

在这方面迫切需要你的帮助。

此致、

Archana Rao