大家好!

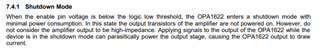

在下面的削波器电路中尝试使用 OPA1622的使能引脚功能时、我遇到了一种非常奇怪的行为:

如上所示、我将 GND 引脚设置为-9V、以便将使能信号参考到该引脚。

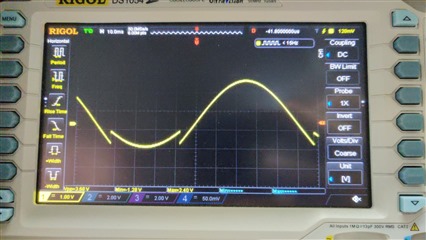

使能信号生成(下面的青色)机制按预期工作、但 OPA1622输出(下面的黄色)不能:

我还应该提到、我将使用2个串联的二极管来保护电源免受反相影响。

我有点不好:)。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Mathieu、

我查看了 OPA1622数据表中出现的所有23个"接地"字样实例。 第7.3.4节接地引脚是指技术规格部分 6.5 -电气特性、其中包括 电气特性表。

仅适用于使能引脚的规格为逻辑高电平阈值(VIH) 典型值0.82V、 逻辑低电平阈值(VIL) 典型值0.78V 以及它们的过热限制。 因此、TI 保证的使能引脚性能基于该表中列出的电压电平。 图43 -使能引脚简化内部原理图是一种简化方法、我们不知道 OPA1622内部连接了什么。 当接地引脚 连接到负电源电压时、可能 会超过内部比较器或放大器限制 、从而改变其 功能。

此致、Thomas

精密放大器应用工程

您好、Mathieu、

是否 在高阻态或50 Ω 负载下捕获了 O 示波器图像? 当 OPA1622输出被禁用时、数据表 显示"在此状态下、放大器的输出晶体管未上电。 但是、不要将放大器输出视为高阻抗。" 可能是输入信号通过运算放大器耦合并出现在输出端。 然后、添加50欧姆负载应将输出电平分压。

我想知道添加低阻抗负载是否会对输出电平产生影响、而不是对高阻抗负载的影响。

此致、Thomas

精密放大器应用工程

您好、Mathieu、

Thomas 今天外出、因此我将在此期间尝试提供支持。

对于50欧姆的情况、这是有道理的;当两个放大器都导通时、有效源阻抗更低。 在本例中、有两个放大器、每个放大器具有100欧姆输出、驱动50欧姆。 因此、相对于 放大器的输出、负载上的有效输出电压将为1/2。 然后、当其中一个放大器被禁用时(假设输出为理想的高阻抗)、输出阻抗变为100欧姆、因此电压将为~ 1/3;第二个示波器快照的情况似乎大致如此。

关于空载情况、我仍然不确定。 必须有一些电流流入禁用的放大器;请注意、OPA1622数据表包含以下摘录:

我不知道流入第二安培的电流是多少;我本不会认为它的电流值与压降看起来的值相同。 此外、我本来希望有一个二极管负载、因此会有恒定电流灌入禁用的放大器、这会导致直流电压变化。 您能否测量第二个(禁用)放大器输出端的电压?

此致、

Mike

您好、Mathieu、

好的,对于电阻器 slang,我会记住这个:)

还需要记住的一点是、输入端子之间仍有二极管。 因此、如果禁用放大器确实将电流灌入其输出、即使在断开100欧姆电阻器上的输出时、它也可能通过输入二极管(从同相输入到反相输入)灌入电流、并通过缓冲器反馈连接流入输出。

源是什么? 它是信号发生器吗? 它还可能具有50欧姆的输出、因此、当负载变化时、它会产生类似的效果。 遗憾的是、您似乎没有"电阻器倾斜"选项来移除输入。 您能否测量本例的输入? 实际上、在输入和输出端子上进行上述相同的测量会有所帮助。

此致、

Mike

尊敬的 Mike:

我认为你是对的! 我修改了上面的电路、在 SMA 连接器和 opa1622输入之间添加了一个1k 电阻器。

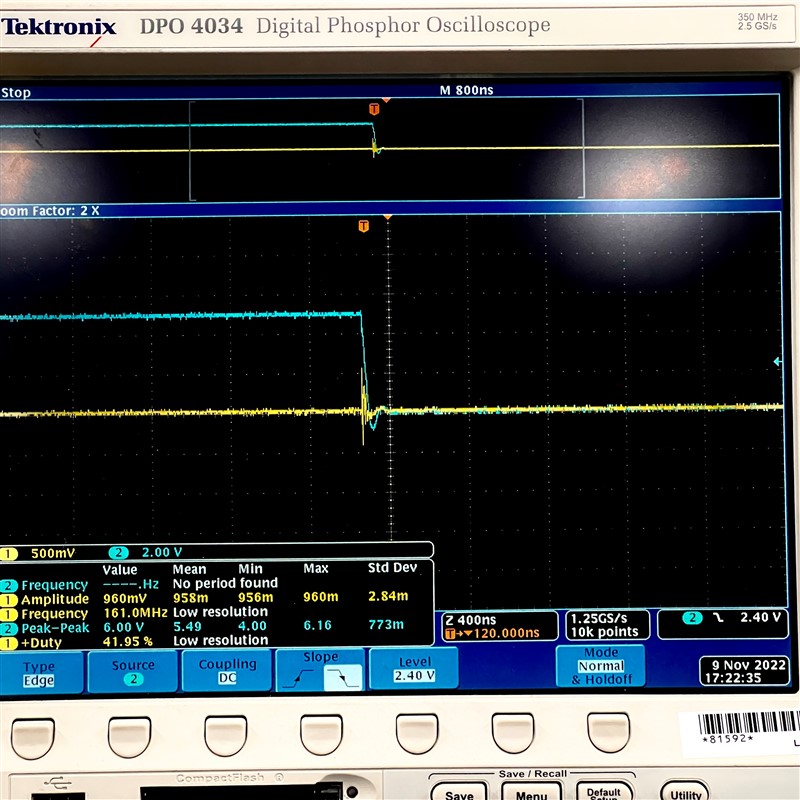

然后、我增大了输入信号的振幅、并在加载50R 时监控电路输出(非常重要的注意事项):

它确实看起来像是一些杂散电流进入+、到-、到输出。

1K 电阻器开始为我的口味增加一点太多的热噪声(4nV/sq (Hz)、除非我弄错了)... 如果我想进一步缓解这一问题、我有哪些选择? 我猜在输出和-之间添加电阻器的效果与在输入和+之间放置相同电阻器的效果完全相同、对吧?

感谢 Mike 的耐心!

您好、Mathieu、

是的、我相信与反相输入串联的1千欧电阻器会产生相同的效果、因为"导通"输入二极管仍会与电阻器串联、就在其另一侧。

我们应用团队的一名研究人员对 OPA1622及其 使能/禁用功能具有更多的经验。 他已经对该功能进行了基准测试、并且更熟悉其特性和行为。 Michael 和我本周一直在尝试协助您的查询、但不知道设备和他所做的一样。 他将在下周回来、并可能能够提供我们所没有的见解。

我想让他有机会回顾您的 e2e 调查、看看他能表达什么想法。

谢谢、Thomas

精密放大器应用工程

Mathieu、

这实际上是针对最近的不同情况而提出的。 正如您提到的、这不是一个常见问题、但对于可能有多少设计、我们会遇到一些可能具有挑战性的情况。 遗憾的是、我没有即时解决方案、一直在与我们的团队讨论这一问题、并尝试在实验室中的不同客户应用中进行实验。 我还将确保我们的团队了解如何使用这些器件、以便我们能够改进未来的器件。 我将在这里与我们的团队一起提出您的设计、看看我们是否会尝试将某种设计确定为解决方案。 我们需要一些时间来讨论这一点。 很抱歉耽误你的时间。 如果您有其他问题或意见、请联系我们。

此致、

Chris Featherstone

Mathieu、

这是一个很好的信息。 感谢您的更新! 我可以在实验室中复制您的场景、并进行相同的测量来分析行为。 我需要大约一个半星期来完成这项工作。 相对于放大器的总负载高于32欧姆负载(1k + 50欧姆)。 我将通过这种方式来了解这是否会影响延迟。 您是否在最靠近运算放大器的1k 欧姆侧与连接器 J2上看到了差异?

此致、

Chris Featherstone

您好、Mathieu、

我使用数据表中列出的条件密切复制了典型特征曲线(图47)。 我也能够与您的结果非常匹配。 主要区别在于、输出电压为中间电源或0V、其中一个实例(数据表)为0V、另一个实例出现在0V 以外的输出电压。

匹配产品数据表:

将输出电压驱动至0V 以外的值:

图47是特定条件下的典型特征曲线。 我们已经看到其他器件上的关断时间变化以及根据数据表测试条件调整参数的情况。 这也说明了与 CMOS 级相比完全关断双极级的挑战。 在双极中、施加信号时始终存在一些低电平偏置、因此我们声明在关断模式下不应将输出级视为高阻态。 不过、我们希望添加此功能、以便工程师可以自行决定将器件置于低功耗状态、从而节省功耗。

如果可以在您的应用电路上提供进一步帮助、请告诉我。

此致、

Chris Featherstone