Other Parts Discussed in Thread: CC8520, TLV320DAC32

主题中讨论的其他器件:CC8520、

我有一个 CC8520接收无线音频并将 I2S 提供给 TLV320DAC32。 CC8520是 I2S 主器件。

我的 TLV320DAC32输出中有大量的嘶嘶声。 言语容易理解、但嘶嘶声让人难以听见。

我在数字麦克风上拍摄了 I2S 总线的屏幕截图、并对其进行了一些推音。 这个 I2S 波形对我来说非常安静、但我听到了嘶嘶声。

e2e.ti.com/.../TLV320DAC32_5F00_I2S_5F00_diff.txtIf 我将 DAC_L 输入静音至 HPLOUT、嘶嘶声消失(以及来自麦克风的所有声音)。

所以我认为问题是这3件事之一

1.麦克风 CC8520源上的实际模拟噪声

接收器 CC8520接收器上的实际模拟噪声

3. DAC32配置不正确的伪影

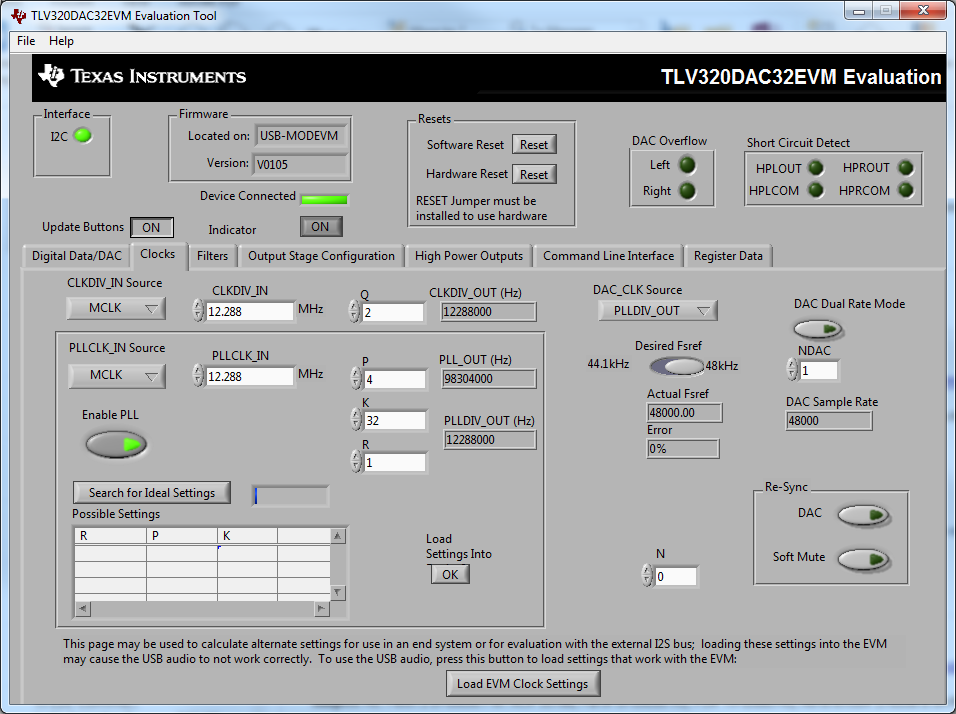

我认为#3是最可能的,因为我已经将源和接收一起测试,作为一个馈送 DAC 内衬输入的系统,并且整个系统没有噪声。 我不确定如何配置 I2S。

谢谢、

Arthur