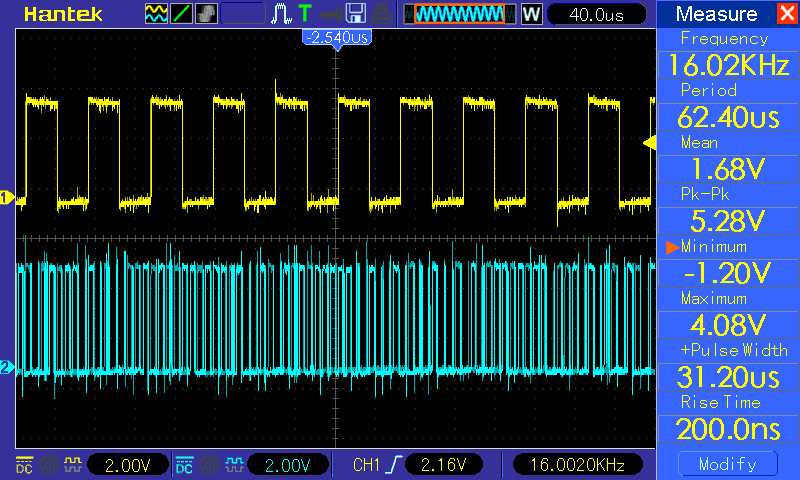

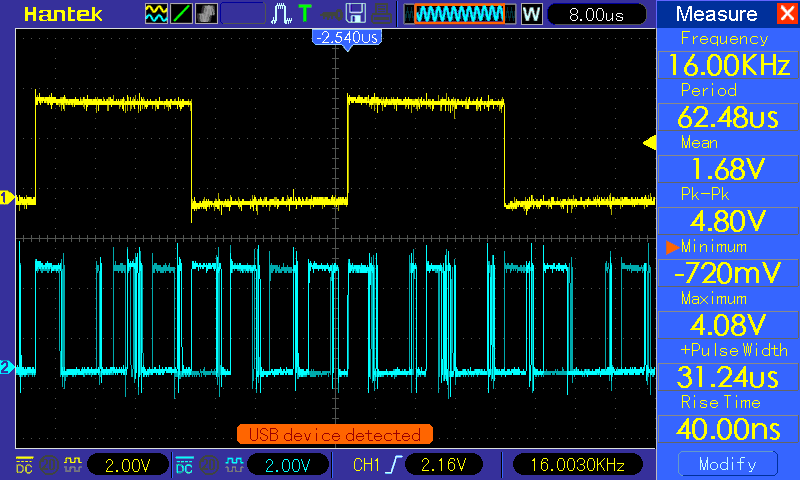

我目前正在使用2个 PCM186 (一个在主器件上配置,另一个在从器 件上配置);两者都配置如下:TDM 数据输出,4个通道(16kHz),字到字时钟(LRCK)为256,采样为32位。 主器件有一个12.288MHz 的外部时钟。 从器件和主器件数据(引脚18)、BCK (引脚17)和 LRCK (引脚16)连接在一起。 主器件工作正常;但是、对于从器件寄存器0x74、表示我具有 无效的 SCK 比率或 LRCK 停止(0x47)。

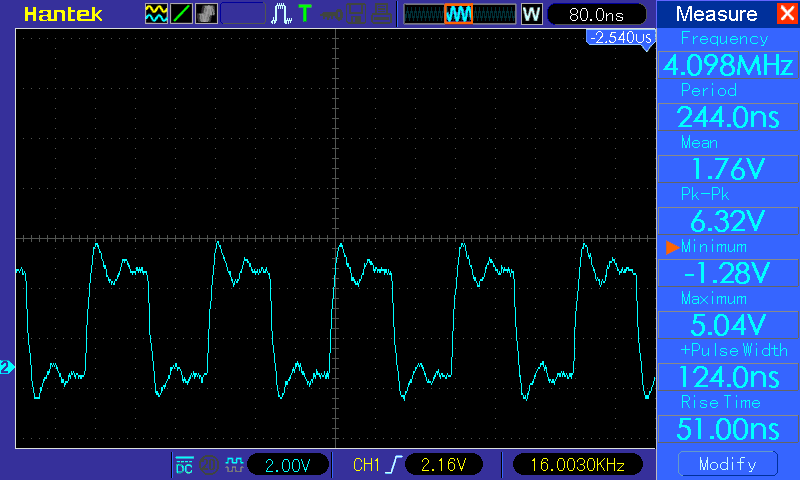

- BCK = 4.096Mhz、在32位时采样16K

- 能否有人验证下面我的从器件寄存器值。 提前感谢您。

- {0x0B、0x03}、//接收 PCM 字长- 32位;TDM_LRCK_MODE - LRCK 的占空比为1/50;立体声 PCM 字长- 32位;串行音频接口格式- TDM/DSP (需要256F BCK)

{0x0C、0x01}、//选择 TDM 传输数据。 01:4通道 TDM

{0x0D、0x80}、// TX_TDM_OFFSET[7:0]- 0x80 bck -只适用于从芯片

{0x0E、0x80}、// RX_TDM_OFFSET[7:0]- 0x80 bck -只适用于从芯片

{0x20、0x42}、// PLL (与 bck PLL 模式一样)

{0x21、0x0B}、// 0x03 DSP1时钟分频器值3:1/4

{0x22、0x17}、// DSP2时钟分频器值7:1/24 -

{0x23、0x2F}、// ADC 时钟分频器值15:1/48 -

{0x28、0x03}、//启用 PLL、PLL 参考时钟选择- SCK -

{0x29、0x01}、// PLL P-Divider 值-

{0x2A、0x01}、// PLL R-Divider 值-

{0x2B、0x17}、// PLL J.D-Divider 值的整数部分-

{0x2C、0x00}、// PLL J.D-Divider 值的分数部分。 (最低有效位)

{0x2D、0x00}、// PLL J.D-Divider 值的分数部分。 (最高有效位、[13:8]) - 请参阅原理图-主器件上的24MHz 已替换为12.288MHz