我们希望在时钟从模式下运行 TLV320adc5140、在 TDM 模式下运行3个 TLV320 x 4通道。

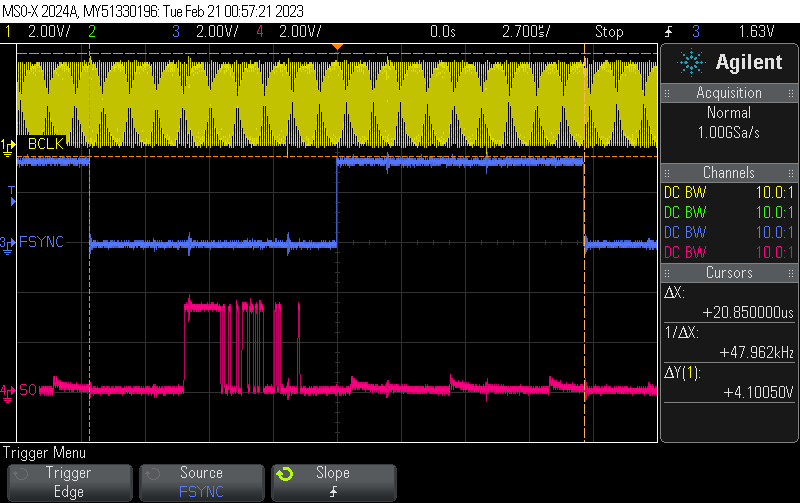

我们尝试了2种设置1) 50kHz FSYNC、12、8MHz BCLK、禁用自动时钟、2) 48kHz、12、288MHz 自动时钟启用。

在这两种情况下、来自内部通道4的数据在所有3个 ADC 上均为零(或 FFFF)。 如果我们将读取的通道4数据移动到另一个时隙、则通道4的问题仍然存在。

在这两种情况下、寄存器 ASI_STS_ADDRESS 的读出均提供0xFFh、这意味着 FSYNC 到 BCLK 以及频率范围没有有效的分频器值。

在50kHz 模式下运行时、我们添加了:

TLV320Write (AD、0x1f、0xA0);// PDMCLK_CFG 配置:MDIV_EN = 0x80、MDIV_VALUE = 0x20 (MDIV 除以8)。

对通道1上的实际数据正弦波转换进行测试效果良好。

随附48kHz 设置的示波器图片。 我们已将设置与 PurePath 仿真进行了仔细比较。

问题 a)我们是否有正确的条件读取1)和2)时钟设置中 ASI_STS_ADDRESS 的时钟估算器值?

问题 b)为什么我们无法读取通道4 ADC 值?

e2e.ti.com/.../TLV320adc-e2e.txt