您好!

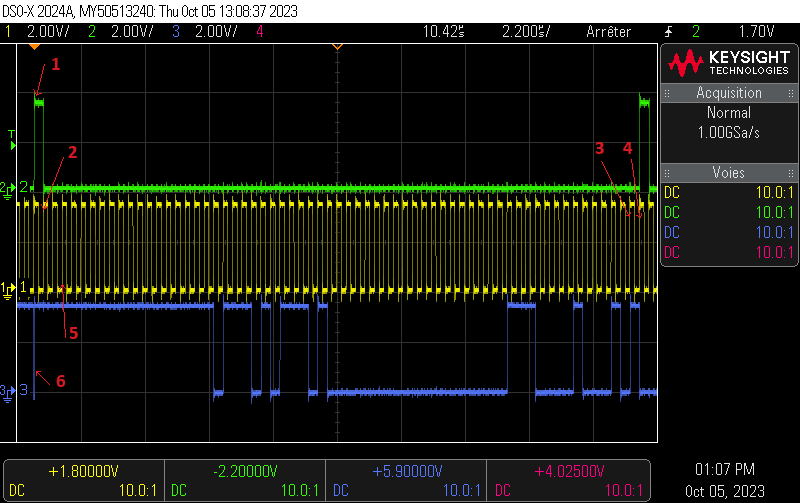

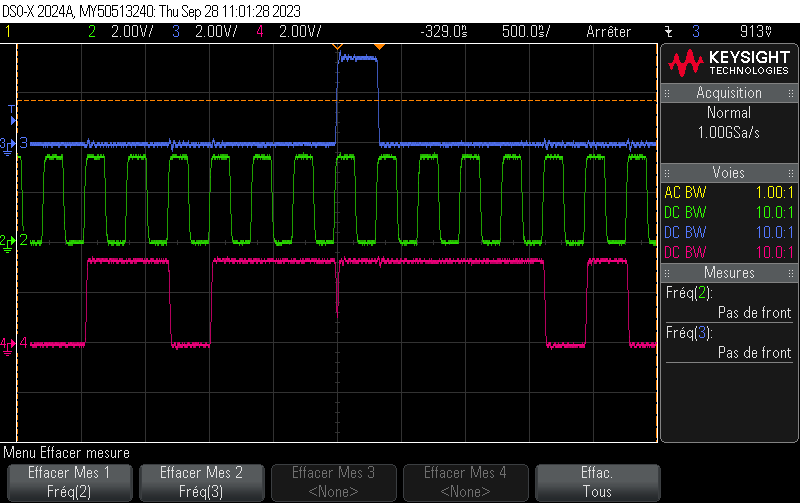

我正在以连接到 STM32处理器的从模式使用 TLC320ADC6140。 TDM 模式、2个32位时隙、无 TX 偏移、FS、BCLK 的默认极性。 FSYNC 速率48kHz 和 BCLK 3.08MHz。

首先、测试效果很好、结果符合预期。

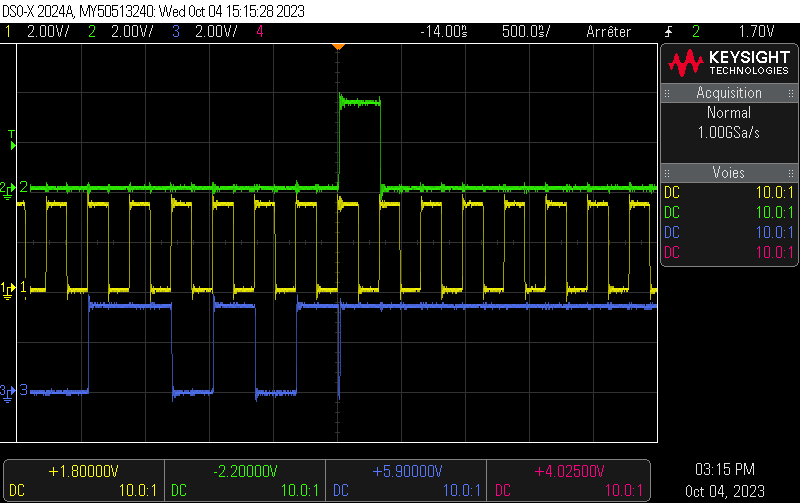

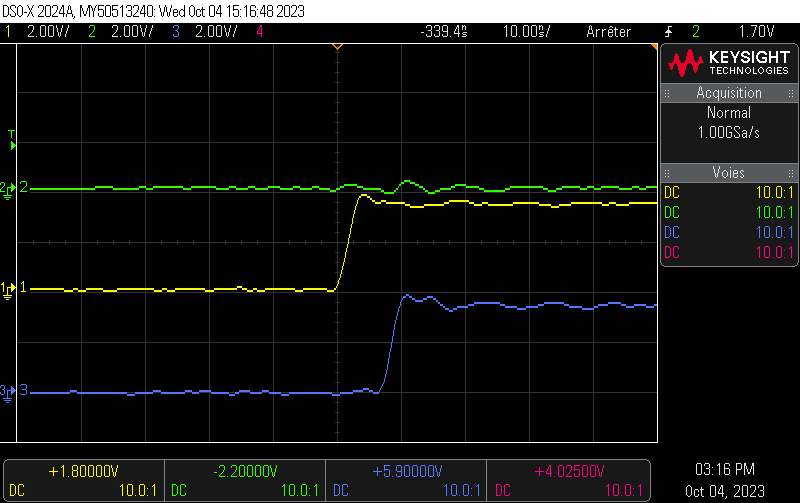

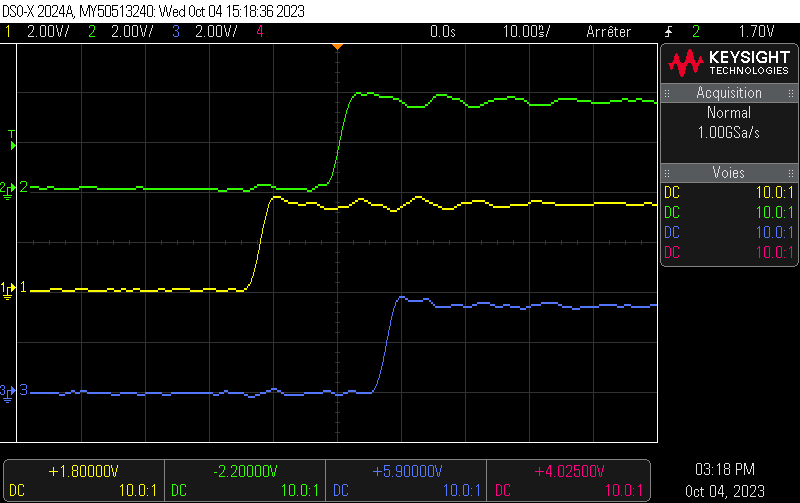

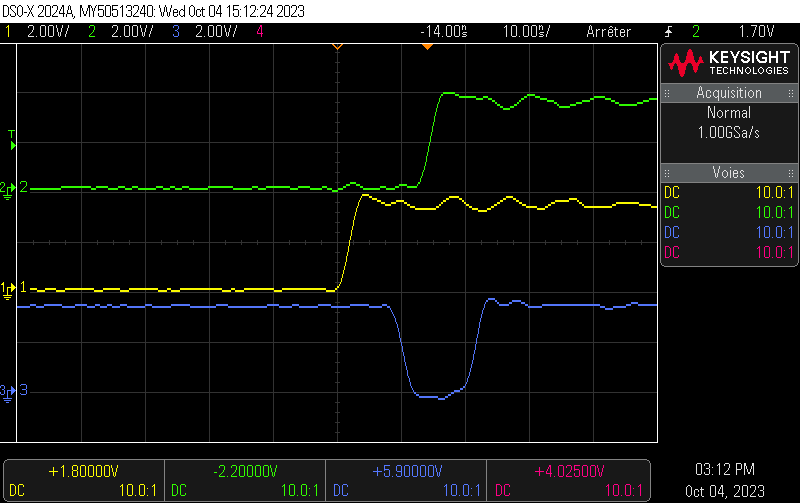

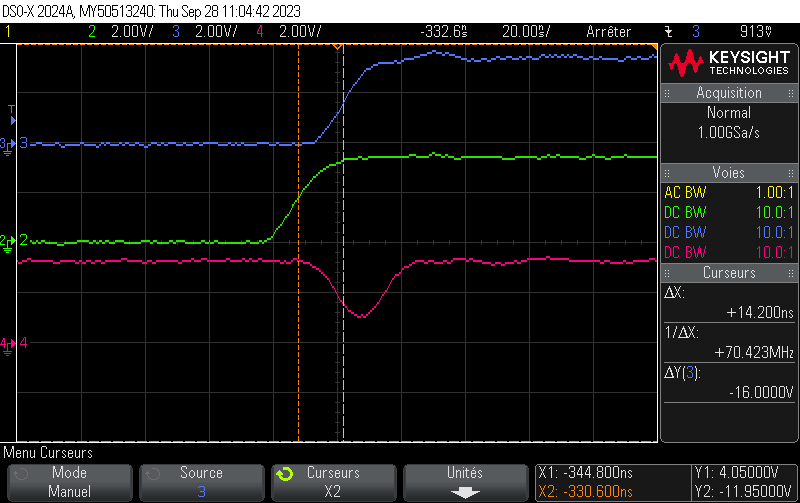

在示波器屏幕上、我们可以看到 FSYNC 在 BLCK 边沿后约15ns 上升。 我们可以在屏幕上看到、TLV 开始在 BCLK 边沿上将其输出更新为0 (void fill)、 但15ns 后、当 DOUT 信号仍下降为0时、会出现 FSYNC 边沿、输出立即更新为时隙0的 MSB 值。

蓝色= FSYNC、绿色= BCLK、红色= SDOUT。

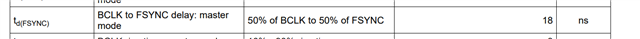

我们可以阅读第8.3.1.2.1节:

"在 TDM 模式、也称为 DSP 模式中、FSYNC 的上升沿首先从时隙0数据开始数据传输。 {...} FSYNC 和每个数据位(TX_OFFSET 等于0时、时隙0的 MSB 除外)在 BCLK 的上升沿发送"

说明 SDOUT 信号在 BCLK 的上升沿更新、时隙0的 MSB 除外、但没有更多说明。 FSYNC 的上升沿似乎覆盖了 BLCK 边沿并强制 SDOUT 更新、我说得对吗?

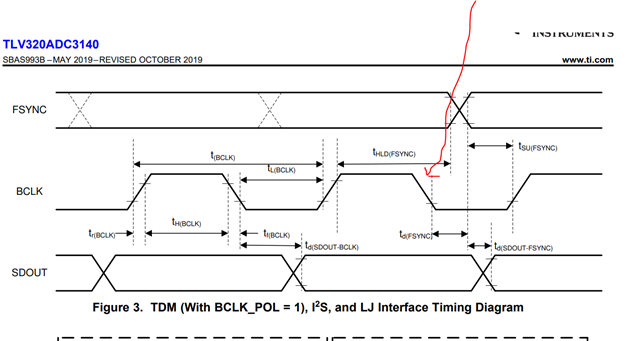

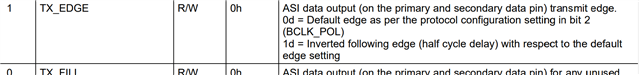

但我不确定 FSYNC / BCLK 边沿计时的裕度。 TLC 数据表未提供很多同步记录、仅提供了当 BCLK_POL = 1时 TDM 模式的时钟、不知道如何在 BCLK_POL = 0时将其与 FSYNC 边沿相关联。

如果 FSYNC 边沿在 BLCK 边沿之后过早 出现或在 BLCK 边沿之前出现(设备或布局容差),会发生什么情况? 是否有释放时隙0的 MSB 的风险(它将在 FSYNC 边沿上传输、但在下一个 BLCK 边沿上被下一个数据位取代)?

如果我在 FSYNC 上添加一个较小的 RC 以确保 BCLK 上升和 FSYNC 上升之间的最小延迟(每条线路上已经有100R+22pF 的延迟),我是否应该处于一个更安全的条件?

谢谢!

奥勒良