主题中讨论的其他器件: PCM1680、PCM4104、 PCM1690、PCM5121

尊敬的:

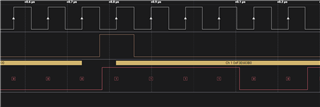

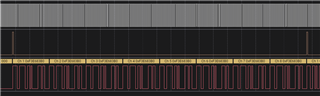

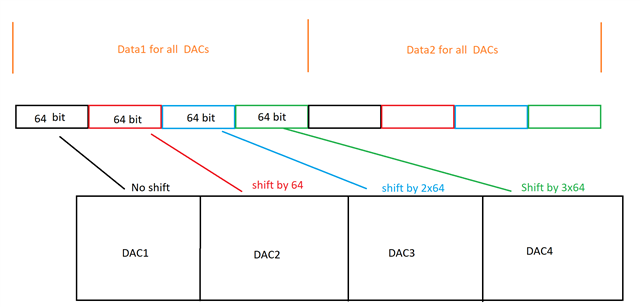

我们在由48kHz 32位音频样本组成的 TDM 总线上使用 PCM5122 4次。

每个 DAC 的配置相同、除了移位寄存器41外、寄存器也相同。

DAC 1 = 0时的 I2S 移位寄存器

DAC 2 = 64时的 I2S 移位寄存器

DAC 3 = 128时的 I2S 移位寄存器

DAC 4 = 192时的 I2S 移位寄存器

在 TDM 总线上、每个帧的每个时隙(总共8个)具有相同的值。

因此、每个输出必须具有相同的信号。

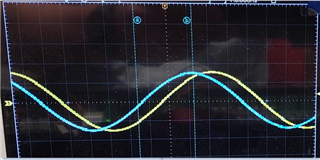

输入和输出是同相输入中的左右通道、

对于 DAC2、DAC3、DAC 4都是同相通道。

但不适用于 DAC1和所有其他 DAC/通道。

仅当我们在相位寄存器41中设置值0时、输出信号才不更加同步。

不同的是1 LRCLK。

因此、我们无法理解只有 DAC1与其他通道不同相。

如何解决此问题?