https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1295262/pcm1840-as-slave-with-pcm1690-dac

器件型号:PCM1840主题中讨论的其他器件:PCM1690、

大家好!

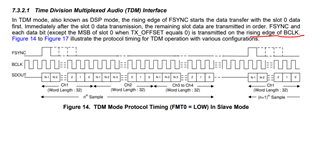

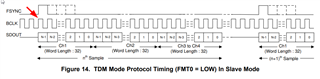

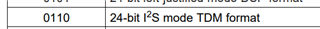

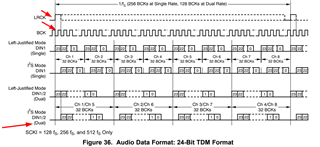

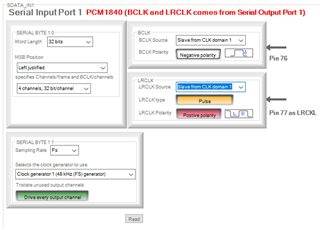

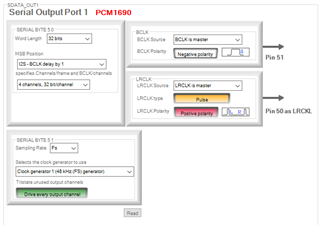

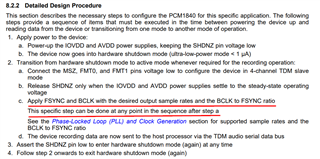

我们使用 PCM1840作为 ADC、而使用 PCM1690作为 DAC。 对于 PCM1840、我们已将其配置为从模式(采用时分多路复用(TDM)模式的4通道输出)。 对于 PCM1690、我们已将其配置为从模式24位 I2S 模式 TDM 格式。 下图显示了我们的配置。

时钟在 ADC 和 DAC 之间共享、并由用作时钟主器件的 DSP 驱动。 我们感到奇怪的是、PCM1690似乎需要正 BCLK、而 PCM1840似乎需要负 BCLK。

- q1:您能否告知我们在 PCM1840和 PCM1690中对位进行采样的时钟转换时间?

我们为使其工作所做的是以下几点。

在 DSP 数据输出端、我们以 I2S 模式发送数据、并将时钟设置为负极性。 在正到负转换时对位进行采样。 这应该能够完美地满足 PCM1690规范、但这些时钟也会发送至 PCM1840、当然 SDATA 除外。 在 DSP 数据输入侧、我们对左对齐进行采样。 目前、我们还在正到负转换时进行采样。

- Q2:在从负到正的转换上采样是否更有意义(这就是为什么我们需要知道 PCM1840的采样点)?

- Q3:到目前为止,这一切看起来都是有效的,但我们想知道,如果你在这里看到任何潜在的风险,因为两个芯片的时钟要求似乎是不同的?

PCM1840

PCM1690

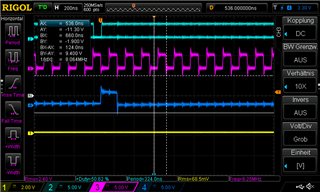

DSP 设置:

除了这个主题、有时 PCM1840会出现一些奇怪的行为。

当我们启动系统时、ADC 锁定到时钟似乎需要超长的时间。 我们重新检查了启动行为、一切看起来都像指定的一样、除了2个点:

-点1和 Q4:是 BCLK 有一个负极比正,如上所述。 这是否会造成这样的问题?

-点2和 Q5:在我们将 ADC 从重置中释放之前,时钟正在运行。 数据表的第28页提到、在步骤 a 后、时钟应首先激活。这真的是必需的吗? 因为当 ADC 以从模式运行时、这并不容易。

此致、

埃里克