您好!

TLV320ADC6120未使用该代码将音频通道分配到指定的时隙

//***** ASI_CH1通道1

//位7-6 = 00 |保留写入00

// bit 5-0 = 000000 | 0d = TDM 为时隙0或 I2S、LJ 为左时隙0

// bin = 00000000十六进制= 0x00

ADC_I2C_Write (ASI_CH1、0x00);

//***** ASI_CH2通道2

//位7-6 = 00 |保留写入00

//位5-0 = 000001 | 1d = 1d = TDM 是时隙1或 I2S、

// bin = 00000001十六进制= 0x01

ADC_I2C_Write (ASI_CH2、0x01);

我认为设置代码有问题、I2S 模式下只有1个插槽填充了来自 ADC 的 SDO 数据

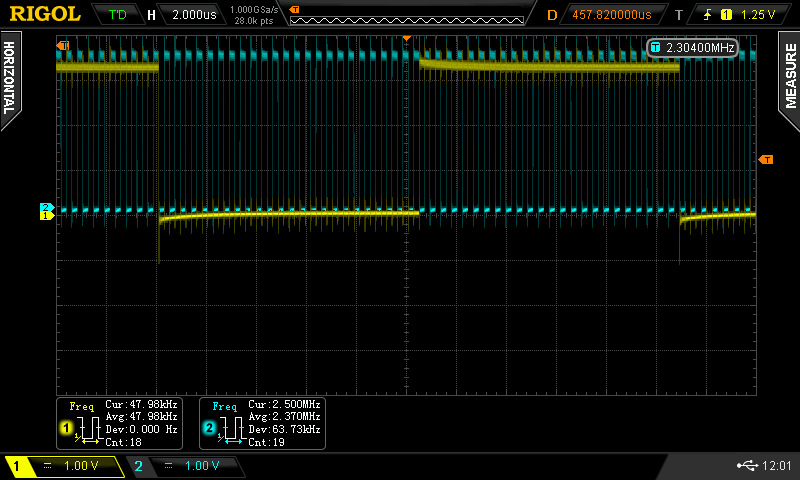

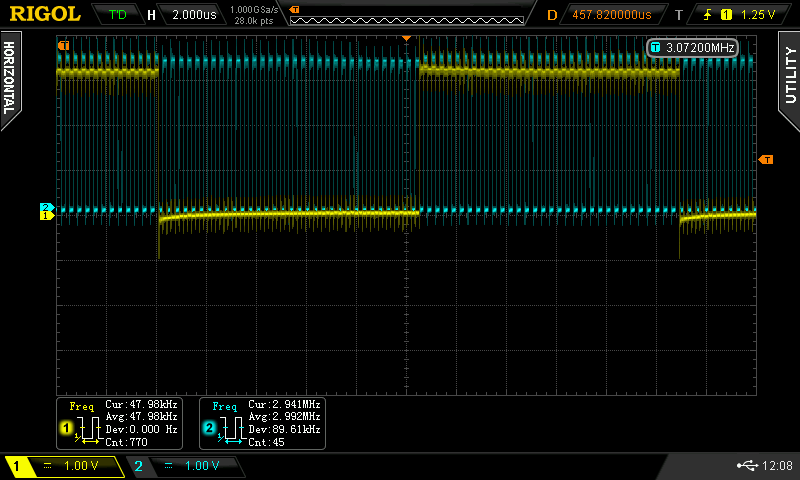

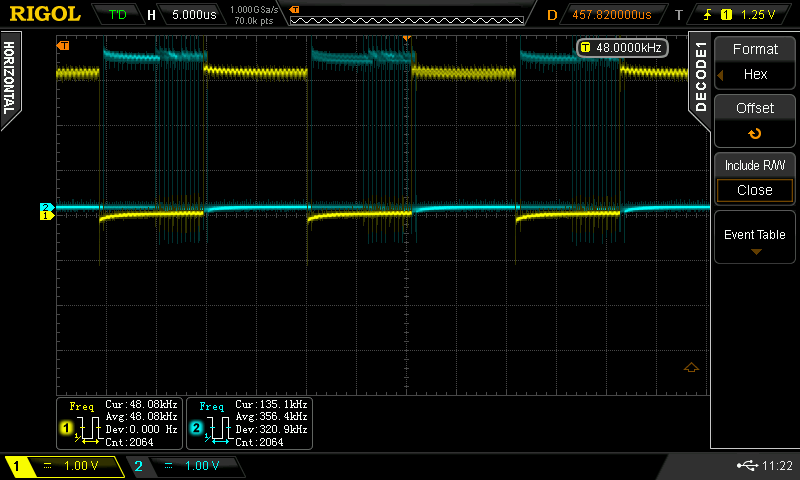

这里是 FSYNC 和 ADC SDout。

插槽0中有音频样本, 插槽1中无音频样本

我正在自动模式下使用 PLL、器件应该是主器件。 I2S 2通道。

这里是我的设置代码;

/**** 接通 ADC 电源***** /

/*等待电源稳定*/

osDelay (250u);/* 250ms。 */

/*使用 MOSFET 为 ADC 上电*/

hardware_adcPowerControl (真);

/*等待 ADC 上电*/

osDelay (250u);/* 250ms。 */

/*###################################### ADC TLV320ADC6120设置################################ */

//注册页面

//页0x00正常设置寄存器,

//页0x01 VAD 语音活动检测

//页0x02可编程系数寄存器:

//页0x03可编程系数寄存器:7-12

//页0x04混频器设置

/*转到第0页*/

ADC_I2C_Write (PAGE_CFG、0x00);

// SW_RESET 寄存器(地址= 0x1)[复位= 0x0]

ADC_I2C_Write (SW_RESET、0x01);

osDelay (20U);/* 10ms。 */

/*转到第0页*/

ADC_I2C_Write (PAGE_CFG、0x00);

//通过使用内部 Areg 对 P0_R2进行 I2C 写入来唤醒器件

//位7 = 1 | 1d =使用片上稳压器在内部生成的1.8 V Areg 电源(当 AVDD 为3.3V 时使用该设置)

// bits 6-5 = 00 |保留位;只写复位值0

// bits 4-3 = 01 | 0d = 3.5ms 的 VREF 快速充电持续时间(典型值)| 3d = 100ms 的 VREF 快速充电持续时间(典型值)

//位2 = 0 | 0d =禁用 I2C 广播模式

// bit 1 = 0 |保留位;写入0

//位0 = 1|1d =器件未处于睡眠模式

// bin 10001001十六进制0x81

ADC_I2C_Write (SLEEP_CFG、0x81);

osDelay (1U);/* 1ms。 */

//*********** GPIO_CFG0寄存器*****

//位7-4 = 1010 | 10d = GPIO1配置为主时钟输入(MCLK)

// bit 3 = 0 |保留位;写入0d

//位2-0 = 010 | 2d =驱动低电平有效和弱高电平有效

// bin 10100010十六进制= 0xA2

ADC_I2C_Write (GPIO_CFG0、0xA2);

//***** MST_CFG0寄存器*****************

//位7 = 1| 1d =器件处于主模式(BCLK 和 FSYNC 都由器件生成)

//位6 = 0 | 0d =启用自动时钟配置

//位5 = 0 | 0d =在自动时钟配置中启用 PLL

//位4 = 0| 0d =当在主模式下从器件传输时、不强制 GATE BCLK 和 FSYNC

//位3 = 0 | 0d = FS 是48kHz 的倍数(或子倍数)

//位2-0 =111 | 7d = 24.576 MHz // 1d = 12.288 MHz MCLK_FREQ_SEL

// bin = 10000001十六进制= 0x81 //自动时钟配置12.288mhz oscilator

// bin = 10000111十六进制= 0x87 //自动时钟配置24.576mhz oscilator

ADC_I2C_Write (MST_CFG0、0x81);

//***** MST_CFG1寄存器*****************

// bits 7-4 = 0100 | 4d = 44.1kHz 或48kHz FS_RATE 页0

// bits 3-0=0011|4D= 64|3D= FSYNC 周期内48:N BCLK 时钟的比率

// bin = 01000100十六进制= 0x44 64 bclks、fsync

// bin = 01000011十六进制= 0x43 fsync 中的48 bclk

ADC_I2C_Write (MST_CFG1、0x43);

/*转到第0页*/

// ADC_I2C_Write (PAGE_CFG、0x00);

//***** IN_CH_EN 寄存器输入通道配置卡

//位7 = 1 | 1d =通道1启用

//位6 = 1| 1d =通道2启用

//位5 = 0 | 0d =通道3被禁用

// bit 4 = 0 | 0d =通道4禁用

// bits 3-0 = 0000 |保留写入0000d

// bin = 11110000十六进制= 0xC0

ADC_I2C_Write (IN_CH_EN、0xC0);

//***** BIAY_CFG 寄存器

// 7位= 0 |保留写入0

// 6-4位= 000 | 0d =麦克风偏置设置为 VREF (2.750V、2.500V 或1.375V)

// 3-2位= 00 |保留写入00

// 1-0位= 00 | 0d = VREF 设置为2.75V、以支持差分输入2 VRMS 或单端输入1 VRMS

// bin = 00000000十六进制= 0x00

ADC_I2C_Write (BIAS_CFG、0x00);

// CLK_SRC 寄存器(地址= 0x16)

//位7 = 0 | 0d = 0d = BCLK 用作音频根时钟源

//位6 = 0 | 0d = 0d = MCLK 频率基于 MCLK_FREQ_SEL (P0_R19)配置

// bit 5-3=011 | 1d = 256 12.288mhz | 3d = 512 ( 24.576mhz )

//位2 = 0 |保留写入0

//位1 = 0| 0d =不反转用于 FSYNC 生成的 BCLK 极性

// bit 0 = 0 |保留写入0。

//位00011000十六进制= 0x18

// ADC_I2C_Write (CLK_SRC、0x18);//在自动模式下启用 PLL,无需写入此地址?

//***** 具有32位/通道 SAI 字的 ASI_CFG0寄存器 I2S 模式

// bits 7-6 = 01 | 1d = I2S 模式

// bits 5-4 = 10| 3d =输出通道数据字长设置为32位| 2d =输出通道数据字长设置为24位

//位3 = 0 | 0d =根据标准协议 FSYNK 默认极性

//位2 = 0 | 0d =根据标准协议确定的 BCLK 默认极性

//位1 = 0 | 0d =默认边沿、符合位2中的协议配置设置(BCLK_POL)

// bit 0 = 0|0d =始终为未使用的周期发送0,为 hi-Z 使用1

// bin = 01110001十六进制= 0x70 // 32位字

// bin = 01100000十六进制= 0x60 // 24位字

// bin = 01000000 hex = 0x40 // 16位字

ADC_I2C_Write (ASI_CFG0、0x60);

// ASI_CFG1寄存器

// bit 7 = 0 |默认值0d =发送 LSB 一个完整周期

//bits 6-5 =00 |默认值0d =始终禁用总线保持器

// bits 4-0 = 00000 | 0d = ASI 数据 MSB 位置无偏移并遵循标准协议

// ADC_I2C_Write (ASI_CFG1、0x00);

//***** ASI_OUT_CH_EN 寄存器*****

//位7 = 1 | 1d =启用通道1输出时隙

//位6 = 1|1d =启用通道2输出时隙

//位5 = 0 | 0d =禁用通道3输出时隙

//位4 = 0 | 0d =禁用通道3输出时隙

// bits 3-0 = 0000 |保留写入0000

// bin = 11000000十六进制= C0

ADC_I2C_Write (ASI_OUT_CH_EN、0xC0);

//***** ASI_CH1通道1

//位7-6 = 00 |保留写入00

// bit 5-0 = 000000 | 0d = TDM 为时隙0或 I2S、LJ 为左时隙0

// bin = 00000000十六进制= 0x00

ADC_I2C_Write (ASI_CH1、0x00);

//***** ASI_CH2通道2

//位7-6 = 00 |保留写入00

//位5-0 = 000001 | 1d = 1d = TDM 是时隙1或 I2S、

// bin = 00000001十六进制= 0x01

ADC_I2C_Write (ASI_CH2、0x01);

//**** CH1_CFG0寄存器字段说明

//位7 = 0| 0d =麦克风输入,1d =线路输入

// bits 6-5 = 01 | 1d =模拟单端输入| 0d =模拟差分输入

//位4 = 0 | 0d =交流耦合输入| 1d =直流耦合输入

// BITS 3-2 = 0 | 0d =典型2.5-kΩ 输入阻抗| 1d =典型10 - kΩ 输入阻抗| 2d =典型20 - kΩ 输入阻抗

//位1 = 0 |保留写入0

// bit 0 = 0 | 0d = DRE/AGC/DRC 被禁用| 1d =根据寄存器108中位3的配置启用 DRE 或 AGC 或 DRC (P0_R108)

// bin = 00100000十六进制= 0x20

ADC_I2C_Write (CH1_CFG0、0x20);

//**** CH2_CFG0寄存器字段说明

//位7 = 0 | 0d =麦克风输入

// bits 6-5 = 01 | 1d =模拟单端输入| 0d =模拟差分输入

//位4 = 0 | 0d =交流耦合输入| 1d =直流耦合输入

// BITS 3-2 = 0 | 0d =典型2.5-kΩ 输入阻抗| 1d =典型10 - kΩ 输入阻抗| 2d =典型20 - kΩ 输入阻抗

//位1 = 0 |保留写入0

// bit 0 = 0 | 0d = DRE/AGC/DRC 被禁用| 1d =根据寄存器108中位3的配置启用 DRE 或 AGC 或 DRC (P0_R108)

// bin = 00100000十六进制= 0x20

ADC_I2C_Write (CH2_CFG0、0x20);

// CH1_CFG1寄存器

//位7 - 1 = 1010100 | 84d =通道增益设置为42dB

//位0 = 0 | 0d =正符号通道增益

// bin 10101000十六进制= 0xA8

ADC_I2C_Write (CH1_CFG1、0xA8);

// CH2_CFG1寄存器

//位7 - 1 = 1010100 | 84d =通道增益设置为42dB

//位0 = 0 |通道1增益符号配置。

// 0d =正符号通道增益

// bin 10101000十六进制= 0xA8

ADC_I2C_Write (CH2_CFG1、0xA8);

//***** PWR_CFG 为 ADC、MICBIAS PLL ETC 寄存器加电字段说明为什么

//位7 = 1 | 1d =加电 MICBIAS

//位6 = 1|1d =为所有启用的 ADC 和 PDM 通道加电

//位5 = 1| 1d = PLL 上电| 0d = PLL 断电

// bit 4 = 0 | 0d =通道上电、如果打开了任何通道记录、则不支持断电

//位3-2 = 00 | 0d =通道1和通道2在使用动态通道上电、启用断电功能时

// bit 1 = 0|0d =禁用 VAD,启用语音活动检测(VAD)算法

//位0 = 0 |保留使用0

//

// bin = 11100000十六进制= E0

ADC_I2C_Write (PWR_CFG、0xE0);// 0xE0为包括 PLL 在内的所有设备上电

//等待 ADC 上电

osDelay (250u);