尊敬的团队:

在通过 I2C 控制端口访问寄存器时、我们的 LSI 无法从器件获取 ACK 这一问题。

这种现象出现在我们的多个测试板上。

在访问 I2C 控制端口时、我们已确认满足数据表中的启动序列。

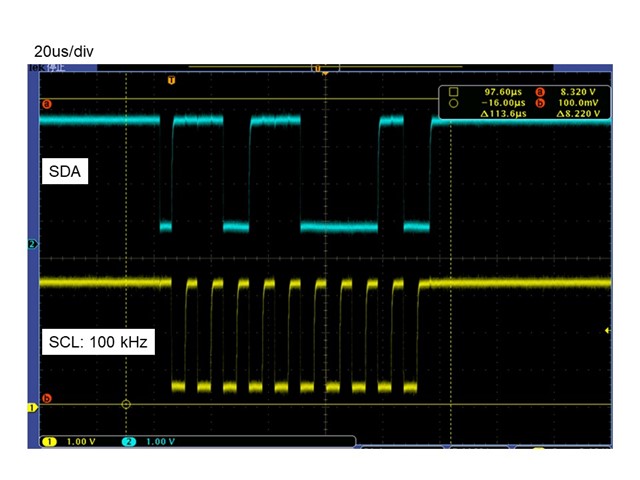

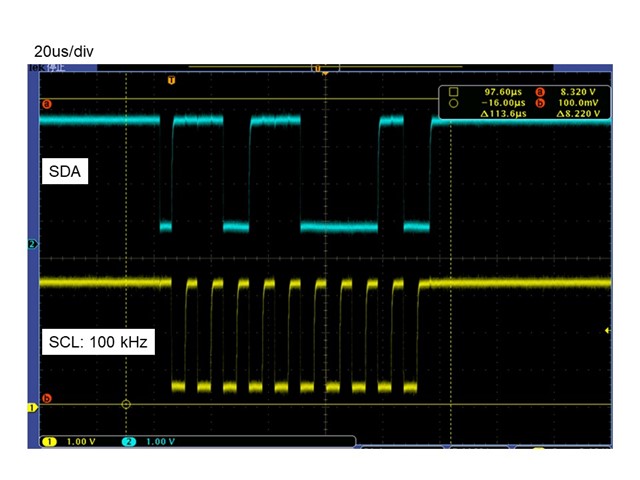

我们附上了测得的波形。 您能介绍一下吗? 从器件地址为0x6C、正确。

我们还确认符合数据表中 I2C 控制端口的交流特性。 因此、我们认为波形不存在问题。

同样、从地址0x6D 不返回 ACK。

您是否报告过任何类似问题?

您能就这个问题提供您的建议吗?

此致、

伊藤琢磨

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的团队:

在通过 I2C 控制端口访问寄存器时、我们的 LSI 无法从器件获取 ACK 这一问题。

这种现象出现在我们的多个测试板上。

在访问 I2C 控制端口时、我们已确认满足数据表中的启动序列。

我们附上了测得的波形。 您能介绍一下吗? 从器件地址为0x6C、正确。

我们还确认符合数据表中 I2C 控制端口的交流特性。 因此、我们认为波形不存在问题。

同样、从地址0x6D 不返回 ACK。

您是否报告过任何类似问题?

您能就这个问题提供您的建议吗?

此致、

伊藤琢磨

高阴影

AVDD 的电压为12V 或24V。 DVDD 为3.3V。

MCLK/SCLK/LRCK 是稳定的。 频率分别为22.579 MHz、2.822 MHz、和44.1kHz。 我们 认为这符合产品说明书。

SPK_SD 的状态为低电平、但即使它为高电平、也无法获得 ACK。

SPK_FAULT 状态始终为高电平。 该引脚未置于低电平。

还有其他我应该检查的东西吗?

高阴影

有两块开发板和三台或更多的原型机。 我们拥有的每个电路板都无法通信。

我们是否能够在 EVM 上放置1个 PCS 来仔细检查? [/报价]我们正在计划尝试您建议的方法。

顺便说一下、我们的 LSI 与 TAS5760M 以外的器件成功实现 I2C 通信。 如果您有这样的经验、能否告诉我您是如何解决的? 有什么我应该检查的吗?

Shadow、

非常感谢您提供的所有建议。

我们重新检查 I2C 数据保持时间、发现它不符合 TAS5760M 数据表中的规格。

在校正数据保持时间后、我能够从 TAS5760M 获得一个 ACK。

我还有一个问题。 TAS5760M 数据表中未提及最大保持时间。

另一方面、根据"UM10204 I2C 总线规范和用户手册"、快速模式下的最大保持时间为0.9us。

您能否告诉我为什么 TAS5760M 数据表和"UM10204 I2C 总线规范和用户手册"存在差异?

如果有差异、以 TAS5760数据表为准吗?

你好,Takuma

我们重新检查了 I2C 数据保持时间,发现它不符合 TAS5760M 数据表中的规范。

校正数据保持时间后、我能够从 TAS5760M 获得一个 ACK。

我们发现了问题。 我很好奇、 您是说启动条件下的保持时间为0.6us? 从波形可以看出、时间似乎足够长、可能 SDA 在 SCL 拉至低电平之前不应上升、这是一个很好的捕捉。

我还有一个问题。 TAS5760M 数据表中未提及最大保持时间。

另一方面,根据"UM10204 I2C-bus 规范和用户手册",快速模式下的最大保持时间为0.9us。

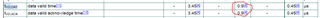

你指的是 TVD;dat 和 TVD;ack 吗? 似乎只有这两个值具有最大0.9us 的要求。

它们都具有注释4、指出"只有当器件不加长 SCL 信号的低周期(TLOW)时才必须满足这个最大值。 如果时钟延伸到 SCL、在它释放时钟前、数据必须在设置时间内有效。"

这里试图说数据设置时间实际上是最重要的值、我们需要首先保证。 在 SCL 的低电平期间、如果需要更改数据、则会出现冲洗/下降时间、而我们要求的 tsu;dat/TVD;dat/tvd;ack 也需要保证数据设置时间。 最小低电平周期 SCL 为1.3us、最大上升/下降时间为0.3us、我们必须保证0.1us 数据设置时间。 因此、如果您计算该值、则仅剩最大值0.9us。 正是处于拐角情况需要此要求。 因此、如果您延长 SCL 的低电平周期、我们通常会遇到的情况是、0.9us 的要求就消失了。 TAS5760数据表仅删除了该要求、我们更旧的器件仍然存在该要求、许多客户提到这一要求毫无意义。

您能告诉我为什么 TAS5760M 数据表和"UM10204 I2C-bus 规范和用户手册"存在差异吗?

如果存在差异、是否以 TAS5760数据表为准?

不应该有太大的差异、TAS6760要求应该全部来自此标准。

我们发现了这个问题,这是个亮点。 我很好奇、 您是说启动条件下的保持时间为0.6us? 从波形可以看出、时间似乎足够、可能 SDA 在 SCL 下拉至低电平之前不应上升、这是一个很好的捕获结果。[/报价]我说过数据保持时间意味着 THD;DAT。 由于"THD;DAT"为负、I2C 通信失败。

[/quote]你指的是 TVD;dat 和 TVD;ack 吗? 似乎只有这两个值具有最大0.9us 的要求。

[/报价]我指的是"THD;DAT"的最大值。 I2C 标准规定"标准模式和快速模式的最大 THD;DAT 可以是3.45 μs 和0.9 μs。"

感谢您的解释。 我能够理解为什么 TAS5760M 中删除了"THD;DAT"的最大值。 我也明白,没有太大的差异。