工具与软件:

大家好、团队

我们的客户在其项目中使用 TLV320ADC6140、并且它们会遇到一些 EMI 问题。

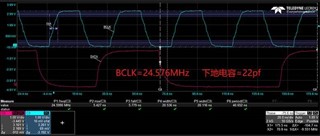

检查后、他们发现问题可能是由 BCLK 引起的(BCLK FW 为24.576M Hz)。 BCLK 波形显示 BCLK 信号波形失真、他们认为它是由信号反射引起的。 如果 PCB 不够好、则具有 信号反射。 但由于 PCB 是固定的、因此他们倾向于向 BCLK 添加一个电容器、以提高信号质量。

请按如下方式检查他们的测试:

测试1:向 BCLK 引脚添加22pF 电容。

测试2:在 BCLK 引脚上添加47PF。

通过22pF 和47pF 电容测试、我们可以看到22pF 电容效果更好、尽管有一些 失真。

我的客户更喜欢就以下问题与我们核实:

1、对于22pF can 47pF cap waveform、您认为该波形会影响 ADC6140的正常运行吗? 请注意、波形有一些 失真、但上升/下降时间可以符合我们的数据表。

2、 BCLK 的最大电容负载是多少? ADC6140数据表显示(在 "7.10时序要求:TDM、I2S 或 LJ 接口"中) ADC6140 I2S 时序测试 基于容性负载为20pF 的条件。 客户更喜欢检查20pF 是否是 BCLK 的最大电容负载?

3、除了 优化 PCB 之外、您还有其他想法来提高 BCLK 性能吗?

谢谢。

G. W