工具与软件:

尊敬的专家

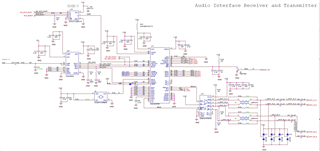

当我们的项目团队使用 TI 的音频收发器 DIX4192芯片时、我们使用 STM32的 SPI 通信。 配置为8位和16位后、我们无法成功发出命令来设置寄存器。

例如、我想将 DIX4192设置为主站并使用 MCLK 作为输出到端口 A 和端口 B 的主时钟、但配置端口后、AB 没有时钟输出。

即使在 DIT 中配置为从端口 A 输出音频到 AESOUT、SYNC 和 RLCK 上也没有时钟。

想了解一下 SPI 配置(CPM Down)和 CS 芯片选型以及复位设置、寄存器配置、每次发送3个字节、发送前减少芯片选型以及发送后提高芯片选型。 还需要哪些其他配置?

您能否向我们发送详细的配置流程? DIX4192是否可以将 I2S 音频配置为 A 输入和 B 输出、以实现自己的 MIC 输入和 SPK 输出?

此外还附加了我们的发送数据

W 7F 00 00

W 03 00 09

W 05 00 29

W 09 00 01

W 0D 00 0B

W 0F 00 12

W 10 00 00 00

W 11 00 00

W 1B 00 0A

W 1C 00 00

W 1D 00 01

W 01 00 3E

W 0E 00 01