Thread 中讨论的其他器件:TAC5212

工具与软件:

大家好!

由于我的应用功耗非常低、我想去掉 TAC5212的 PLL。

我的要求为:

- TAC5212应配置为控制器

- TAC5212应接受14,745,600Hz 的时钟作为 CCLK

- TAC5212应生成 FSYNC = 19,200 Hz 和 BCLK = 1,228,800 Hz

- TAC5212应 在 I2S 模式下发送/接收两个32位数据字

-应禁用 TAC5212的内部 PLL

比率为:

R1 = BCLK/FSYNC = 64、R2 = CCLK/FSYNC = 768

为了努力满足这些要求、我执行了以下操作:

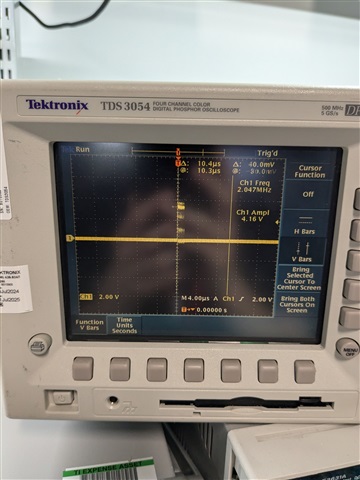

1) 1)作为基准、运行 EVM 用户指南中的 I2C 命令(请参阅下图)、向 GPIO1施加12,288,000Hz 的时钟(CCLK)、并使用示波器监控 FSYNC 信号。

I 测量:FSYNC = 48,000Hz、如预期。

2) 2)修改第0页的寄存器0x32:设置 PASI_SAMP_RATE = 27D = 19,200Hz。 然后将 CCLK 修改为14,745,600Hz。

I measure FSYNC = 23,040Hz。 该值也是预期值、因为 14,745,600600/12,288,000 = 1.2、因此19,200 * 1.2 = 23,040 Hz。

3) 3)修改第0页的寄存器0x32:设置 PASI_SAMP_RATE = 28D = 16,000Hz、因为19,200/1.2 = 16,000Hz。

I measure FSYNC = 19,200Hz。 此时生成的时钟是正确的。

4) 4)通过读取第0页的寄存器0x3E 检查状态。

我读取 PLL_MODE_STS = 0d =在整数模式下使用 PLL。

5) 5)修改第0页的寄存器0x34:设置 PLL_DIS = 1d =禁用 PLL、设置 AUTO_PLL_FR_ALLOW = 0d =禁用 PLL 分数模式。

修改后、FSYNC 上没有信号。

我的问题:我应该在禁用 PLL 后修改其他寄存器吗? 是否有介绍如何摆脱 PLL 的应用手册?

提前感谢您的支持。

BR、

S é bastien