主题中讨论的其他器件: TLV320ADC3101、 CC2564C、 CC2564

您好、专家、

我的客户购买了用于使用 A2DP 接收器进行蓝牙耳机连接测试的 BT-MSPAUDSOURCE 板。

下面我有关于 U12和 U5连接的问题。

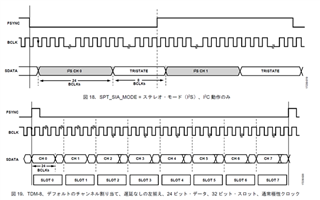

Q1)信号格式 AUD_IN: I2S 格式? 以及使用了哪些位(位数)?

Q2) AUD_CLK 和 AUD_FSYN 的方向: "U12至 U5"或"U5至 U12"?

U12:TLV320ADC3101 U5:CC2560RVM

此致、

Saito